Abbildungsverzeichnis

| Abb. 1: | Das Mainboard und die ausgebauten Komponenten 2.1.1 Erstmal aufschrauben |

| Abb. 2: | John von Neumann (um 1940) 2.1.2 Von-Neumann-Rechner |

| Abb. 3: | Von-Neumann-Architektur 2.1.2.1 Von-Neumann-Architektur | |

| Abb. 4: | Von-Neumann-Architektur 2.1.3 Komponenten eines Von-Neumann-Rechners | |

| Abb. 5: | CPU mit Steuerwerk und Rechenwerk 2.1.3.1 Zentraleinheit / CPU |

| Abb. 6: | Eine einfache Sicht auf die Arbeitsweise des Steuerwerks 2.1.3.1.1 Steuerwerk / Leitwerk |

| Abb. 7: | Steuerwerk mit Befehlszähler und Befehlsregister 2.1.3.1.1 Steuerwerk / Leitwerk |

| Abb. 8: | Eine detailliertere Sicht auf die Arbeitsweise des Steuerwerks 2.1.3.1.1 Steuerwerk / Leitwerk |

| Abb. 9: | Steuerwerk mit Adress- und Datenbus 2.1.3.1.1 Steuerwerk / Leitwerk |

| Abb. 10: | Rechenwerk mit ALU 2.1.3.1.2 Rechenwerk |

| Abb. 11: | Funktionen des Rechenwerks, die vom Steuerwerk in Auftrag gegeben werden können 2.1.3.1.2 Rechenwerk |

| Abb. 12: | Statusbits des Rechenwerks, die vom Steuerwerk ausgewertet werden können 2.1.3.1.2 Rechenwerk |

| Abb. 13: | Speicherwerk mit Bus-System 2.1.3.2 Speicherwerk |

| Abb. 14: | Abbildung zu Aufgabe 2 2.1.3.2 Speicherwerk |

| Abb. 15: | Abbildung zu Aufgabe 4 2.1.3.2 Speicherwerk |

| Abb. 16: | Abbildung zu Aufgabe 4 2.1.3.2 Speicherwerk |

| Abb. 17: | Ein-/Ausgabewerk 2.1.3.3 Ein- / Ausgabewerk |

| Abb. 18: | Gesamtbild eines Von-Neumann-Rechners 2.1.3.4 Gesamtbild eines Von-Neumann-Rechners | |

| Abb. 19: | Arbeitsweise des Steuerwerks II 2.1.3.5 Von-Neumann-Zyklus |

| Abb. 20: | Von-Neumann-Zyklus in der Arbeitsweise des Steuerwerks 2.1.3.5 Von-Neumann-Zyklus |

| Abb. 21: | Von-Neumann-Zyklus 2.1.3.5 Von-Neumann-Zyklus |

| Abb. 22: | Gesamtbild eines Von-Neumann-Rechners 2.1.5 Digitale Schaltungen | |

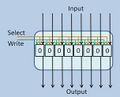

| Abb. 23: | Register mit 8 Speicherzellen 2.1.5.1 Aufbau und Arbeitsweise eines Registers |

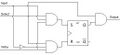

| Abb. 24: | Aufbau einer einzelnen Speicherzelle 2.1.5.1 Aufbau und Arbeitsweise eines Registers |

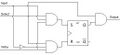

| Abb. 25: | Wahrheitstafeln von UND-Gattern mit zwei bzw. drei Eingängen 2.1.5.1 Aufbau und Arbeitsweise eines Registers | |

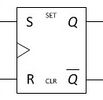

| Abb. 26: | RS-Flip-Flop und die zugehörige Wahrheitstafel 2.1.5.1 Aufbau und Arbeitsweise eines Registers | |

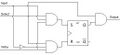

| Abb. 27: | Unterschiedliche Gatter 2.1.6 Gatter | |

| Abb. 28: | Wahrheitstafel für Gatter 2.1.6 Gatter |

| Abb. 29: | Abbildung zu Aufgabe 6 2.2.1 Vom Quellcode zum Prozessor |

| Abb. 30: | Einfacher Befehlssatz 2.2.2 Befehlssatz |

| Abb. 31: | Von-Neumann-Zyklus 2.2.3.4 Das Adressformat und der Von-Neumann-Zyklus |

| Abb. 32: | Einfacher Befehlssatz 2.2.3.5 Aufgaben & Co. zum Befehlsformat |

| Abb. 33: | Abbildung zu Aufgabe 1 2.2.3.5 Aufgaben & Co. zum Befehlsformat |

| Abb. 34: | Der aktuelle Betrachtungsstand: Nicht mehr als ein einfacher Taschenrechner 2.3 Weitere Komponenten der Computerarchitektur |

| Abb. 35: | Stackregister auf der CPU 2.3.1 Stackregister |

| Abb. 36: | CPU mit Basisregister 2.3.2 Basisregister |

| Abb. 37: | CPU mit Limitregister 2.3.3 Limitregister zum Speicherschutz |

| Abb. 38: | CPU mit Interrupt-Controller 2.3.4 Interrupt-Controller |

| Abb. 39: | Interrupt-Controller im Gesamtbild 2.3.4 Interrupt-Controller | |

| Abb. 40: | Abbildung zu Aufgabe 1 2.3.4.3 Quasi-gleichzeitige Ausführung mehrerer Prozesse | |

| Abb. 41: | CPU, Interrupt-Controller, Speicherwerk und weitere Controller mit ihren Komponenten 2.3.4.4 Kommunikation mit E/A-Geräten | |

| Abb. 42: | Allgemeiner Aufbau eines Controllers 2.3.4.4.1 Allgemeiner Aufbau eines Controllers |

| Abb. 43: | Verschiedene Controller mit eigenen Registersätzen 2.3.4.4.1 Allgemeiner Aufbau eines Controllers |

| Abb. 44: | Vereinfachter Rechner, noch ohne DMA-Controller 2.3.5 DMA-Controller |

| Abb. 45: | Vereinfachter Rechner, mit DMA-Controller 2.3.5 DMA-Controller |

| Abb. 46: | Aufbau eines DMA-Controllers 2.3.5.1 Aufbau und Arbeitsweise eines DMA-Controllers |

| Abb. 47: | DMA-Datentransfer als Schleife 2.3.5.1 Aufbau und Arbeitsweise eines DMA-Controllers |

| Abb. 48: | Daten müssen den Umweg über die CPU nehmen 2.3.5.2 Direkt kann wirklich direkt bedeuten | |

| Abb. 49: | Umweg über DMA-Controller 2.3.5.2 Direkt kann wirklich direkt bedeuten | |

| Abb. 50: | Aufbau eines DMA-Controllers 2.3.5.2 Direkt kann wirklich direkt bedeuten |

| Abb. 51: | North- und Southbridge als zentrale Verbindungspunkte 2.3.7 Moderne Bussysteme |

| Abb. 52: | Betriebssystem und Anwendungprogramm(e) vermitteln zwischen Benutzer und Hardware 3.1.3 Zwischen Benutzer und Hardware |

| Abb. 53: | 3.1.10 Kernel-Mode, User-Mode und Systemaufrufe |

| Abb. 54: | 3.2.5.2 Prozesskontrollblock unter Linux |

| Abb. 55: | Prozesszustände mit Übergängen 3.2.7 Prozesszustände | |

| Abb. 56: | Scheduler und Dispatcher werden bei einem Kontextwechsel aktiv 3.2.10 Scheduling | |

| Abb. 57: | Windows 7 Prozessorzeitplanung 3.2.10.2.4 Round Robin |

| Abb. 58: | Windows Server 2008 R2 Prozessorzeitplanung 3.2.10.2.4 Round Robin |

| Abb. 59: | Die im Video gezeigte Seitentabelle 3.3.1.2.1 Einstufige Seitentabellen |

| Abb. 60: | Seitentabelle mit zusätzlicher Spalte für M-Bit 3.3.2.2.2 Das Modifiziert-Bit | |

| Abb. 61: | Seitentabelle mit zusätzlicher Spalte für R-Bit 3.3.2.2.3.2 NRU - Not Recently Used Algorithmus | |

| Abb. 62: | Geräteverwaltung als Schnittstelle zwischen Peripheriegeräten und Betriebssystem 3.4.1 Rolle der Geräteverwaltung |

| Abb. 63: | Treiber als Mittler zwischen Controller und Geräteverwaltung 3.4.3 Gerätetreiber |

| Abb. 64: | Ein initialisierter Controller 3.4.4.1 Initialisierung des Geräte-Controllers | |

| Abb. 65: | Geräte-Manager von Windows 7 3.4.4.2 Gerät dem Betriebssystem bekannt machen |

| Abb. 66: | 'lshw -short' unter Linux 3.4.4.2 Gerät dem Betriebssystem bekannt machen |

| Abb. 67: | Der Treiber als Mittler zwischen Geräteverwaltung und Geräte-Controller 3.4.4.3 Bereitstellen einer Schnittstelle zum Geräte-Controller |

| Abb. 68: | Für jedes Gerät (bzw. Controller) ein eigener Treiber 3.4.4.3 Bereitstellen einer Schnittstelle zum Geräte-Controller |

| Abb. 69: | Ein Interrupt mit seiner zugehörigen Interruptbehandlungsroutine (ISR) unterbricht den Prozess A auf der CPU 3.4.4.4 Interruptbehandlung für ein Gerät | |

| Abb. 70: | Der Treiber als Mittler zwischen Geräteverwaltung und Geräte-Controller 3.4.4.5 Bereitstellen einer Schnittstelle zur Geräteverwaltung |

| Abb. 71: | Zwei Volumes auf drei Partitionen unter Windows 7 3.5.5 Von Windows unterstützte Dateisysteme |

| Abb. 72: | Beispiel einer FAT 3.5.5.1 FAT - File Allocation Table | |

| Abb. 73: | Clusterspur einer Datei in der FAT 3.5.5.1 FAT - File Allocation Table |

| Abb. 74: | Ein Aufruf von 'ntfsinfo.exe c:' unter Windows 7 3.5.5.2 NTFS - New Technology File System |

| Abb. 75: | Um diese Komponente geht es in dieser Aufgabe 4.1 Aufgaben zum Kapitel Vom Anwender zur digitalen Schaltung |

| Abb. 76: | Flip-Flop 4.1 Aufgaben zum Kapitel Vom Anwender zur digitalen Schaltung |

| Abb. 77: | Um diese Komponente geht es in dieser Aufgabe 4.1 Aufgaben zum Kapitel Vom Anwender zur digitalen Schaltung |

| Abb. 78: | Abbildung zu Aufgabe 1 4.2 Aufgaben zum Kapitel Prozessoren und ihre Befehle |

| Abb. 79: | Ein Interrupt mit seiner zugehörigen Interruptbehandlungsroutine (ISR) unterbricht den Prozess A auf der CPU 4.7 Aufgaben zum Kapitel Geräteverwaltung |