2.3.5.1 Aufbau und Arbeitsweise eines DMA-Controllers

| [unmarkierte Version] | [gesichtete Version] |

Keine Bearbeitungszusammenfassung |

Kwastg (Diskussion | Beiträge) |

||

| (8 dazwischenliegende Versionen von 4 Benutzern werden nicht angezeigt) | |||

| Zeile 1: | Zeile 1: | ||

=Aufbau und | <p> | ||

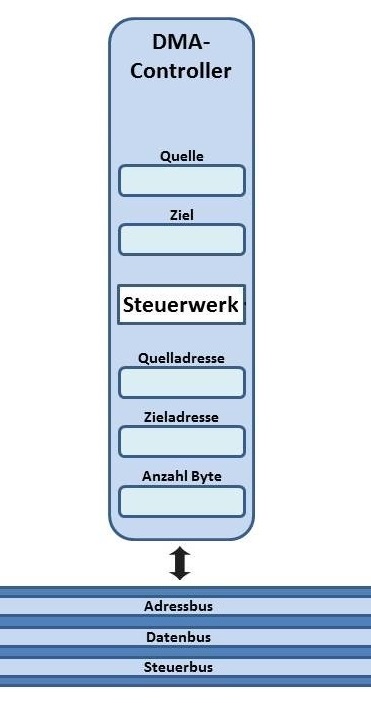

Die folgende Abbildung zeigt den (vereinfachten) Aufbau eines DMA-Controllers. | |||

</p> | |||

<p> | |||

<loop_figure title="Aufbau eines DMA-Controllers" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9783fb9a62"> | |||

[[Datei:DMA-Controller.jpg]] | |||

</loop_figure> | |||

</p> | |||

<br /> | |||

== Initialisierung des DMA-Controllers == | |||

<p> | |||

Bevor die Datenübertragung starten kann, muss der DMA-Controller von der CPU initialisiert werden, d.h. die notwendigen Informationen rund um die zu tätigende Übertragung erhalten. Dies sind: | |||

</p> | |||

<p> | |||

* Quelle:<br />Von diesem Gerät sollen Daten übertragen werden. | |||

</p> | |||

<p> | |||

* Ziel:<br />Zu diesem Gerät hin sollen die Daten übertragen werden. | |||

</p> | |||

<p> | |||

* Startadresse:<br />Ab dieser Adresse auf der Quelle sollen Daten übertragen werden. | |||

</p> | |||

<p> | |||

* Zieladresse:<br />Zu dieser Adresse auf dem Ziel sollen die Daten übertragen werden. | |||

</p> | |||

<p> | |||

* Anzahl Byte:<br />Gibt die Anzahl der Bytes an, die ab Startadresse auf der Quelle zur Zieladresse auf dem Ziel übertragen werden sollen. | |||

</p> | |||

<br /> | |||

== Datentransfer als Schleife == | |||

<p> | |||

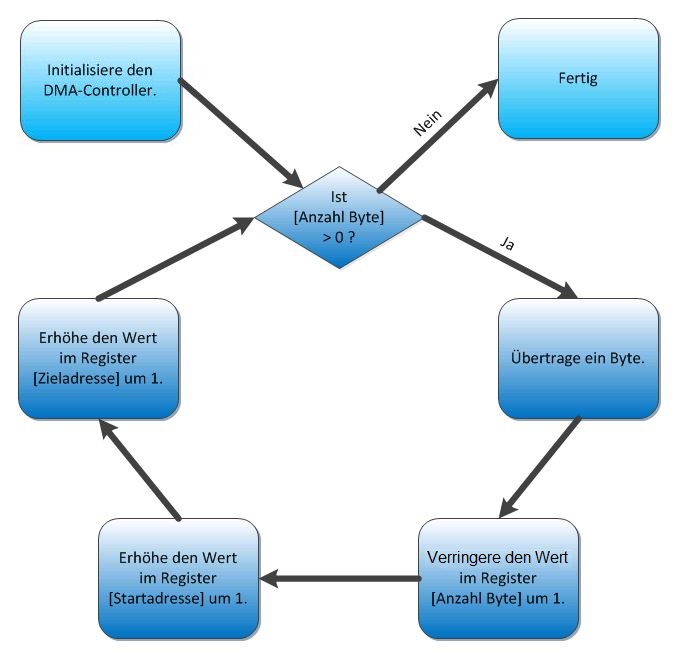

Sobald der DMA-Controller initialisiert ist, kann die Übertragung starten. Dabei wird immerfort eine Schleife durchlaufen, bis alle Byte übertragen sind. | |||

</p> | |||

<p> | |||

<loop_figure title="DMA-Datentransfer als Schleife" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9783fb9a6d"> | |||

[[Datei:DMA-Transfer-2.jpg]] | |||

</loop_figure> | |||

</p> | |||

<br /> | |||

== Aufgabe 1 == | |||

<p> | |||

<loop_area type="task"> | |||

<loop_task title="Start- und Zieladresse ändern sich" id="5fa9783fb9a73"> | |||

<p> | |||

Warum werden beim Datentransfer sowohl die Startadresse als auch die Zieladresse nach jedem übertragenen Byte verändert? | |||

</p> | |||

</loop_task> | |||

</loop_area> | |||

</p> | |||

<br /> | |||

== Aufgabe 2 == | |||

<p> | |||

<loop_area type="task"> | |||

<loop_task title="DMA mit RAM und RAM?" id="5fa9783fb9a78"> | |||

<p> | |||

Quelle und Ziel der Datenübertragung per DMA könnten beispielsweise Festplatte und RAM sein. | |||

</p> | |||

<p> | |||

Aber ist auch denkbar, dass RAM und nochmal RAM die Quelle und das Ziel der Übertragung bilden? | |||

</p> | |||

</loop_task> | |||

</loop_area> | |||

</p> | |||

<br /> | |||

== Aufgabe 3 == | |||

<p> | |||

<loop_area type="task"> | |||

<loop_task title="Datentransfer mit DMA" id="5fa9783fb9a7d"> | |||

<p> | |||

<cite id="5fa9783fb9a82">Brinkschulte+et+al.+2010</cite> zeigen in Kapitel 4.6 mit Abb. 4.53 den grundsätzlichen Aufbau eines DMA-Controllers. | |||

</p> | |||

<p> | |||

Erläutere in deiner Lerngruppe anhand der Abb. 4.53 die [[DMA-Controller#Direct_Memory_Access|aufgelisteten Schritte des Datentransfers mit DMA]]. | |||

</p> | |||

<p> | |||

* Welche Informationen werden in welchen Registern abgelegt? | |||

* Wann werden welche Signale/Informationen über welche Leitungen gesendet? | |||

</p> | |||

</loop_task> | |||

</loop_area> | |||

</p> | |||

<br /> | |||

== Intel 8257 & 8237 Programmable DMA Controller == | |||

<p> | |||

<loop_area type="practice"> | |||

<p> | |||

Der Intel 8257 ist ein bekannter Vertreter aus der Reihe der DMA-Controller. Sein [http://www.threedee.com/jcm/terak/docs/Intel%208257%20Programmable%20DMA%20Controller.pdf Datenblatt] ist noch heute im Internet abrufbar. | |||

</p> | |||

<p> | |||

Eine Weiterentwicklung ist der Intel 8237 ([http://ebookbrowsee.net/8237a-dma-controller-pdf-d198481059 Datenblatt]), der bereits im Jahre 1981 im [http://de.wikipedia.org/wiki/IBM_Personal_Computer ursprünglichen IBM PC] verbaut war. | |||

</p> | |||

</loop_area> | |||

</p> | |||

Aktuelle Version vom 10. November 2020, 16:10 Uhr

Die folgende Abbildung zeigt den (vereinfachten) Aufbau eines DMA-Controllers.

Initialisierung des DMA-Controllers

Bevor die Datenübertragung starten kann, muss der DMA-Controller von der CPU initialisiert werden, d.h. die notwendigen Informationen rund um die zu tätigende Übertragung erhalten. Dies sind:

- Quelle:

Von diesem Gerät sollen Daten übertragen werden.

- Ziel:

Zu diesem Gerät hin sollen die Daten übertragen werden.

- Startadresse:

Ab dieser Adresse auf der Quelle sollen Daten übertragen werden.

- Zieladresse:

Zu dieser Adresse auf dem Ziel sollen die Daten übertragen werden.

- Anzahl Byte:

Gibt die Anzahl der Bytes an, die ab Startadresse auf der Quelle zur Zieladresse auf dem Ziel übertragen werden sollen.

Datentransfer als Schleife

Sobald der DMA-Controller initialisiert ist, kann die Übertragung starten. Dabei wird immerfort eine Schleife durchlaufen, bis alle Byte übertragen sind.

Aufgabe 1

Warum werden beim Datentransfer sowohl die Startadresse als auch die Zieladresse nach jedem übertragenen Byte verändert?

Aufgabe 2

Quelle und Ziel der Datenübertragung per DMA könnten beispielsweise Festplatte und RAM sein.

Aber ist auch denkbar, dass RAM und nochmal RAM die Quelle und das Ziel der Übertragung bilden?

Aufgabe 3

Brinkschulte et al. 2010 zeigen in Kapitel 4.6 mit Abb. 4.53 den grundsätzlichen Aufbau eines DMA-Controllers.

Erläutere in deiner Lerngruppe anhand der Abb. 4.53 die aufgelisteten Schritte des Datentransfers mit DMA.

- Welche Informationen werden in welchen Registern abgelegt?

- Wann werden welche Signale/Informationen über welche Leitungen gesendet?

Intel 8257 & 8237 Programmable DMA Controller

Der Intel 8257 ist ein bekannter Vertreter aus der Reihe der DMA-Controller. Sein Datenblatt ist noch heute im Internet abrufbar.

Eine Weiterentwicklung ist der Intel 8237 (Datenblatt), der bereits im Jahre 1981 im ursprünglichen IBM PC verbaut war.