2.3.7 Moderne Bussysteme

Das bis jetzt erarbeitete Bild eines Computersystems enthält immer noch einen einzelnen Bus, der lediglich in Adressbus, Datenbus und Steuerbus aufgeteilt ist. Bereits im Kapitel Von-Neumann-Flaschenhals wurde anschaulich gezeigt, dass diese Form des Busses sehr schnell überlastet sein kann und sich deshalb nicht zum Bau eines schnellen Gesamtsystems eignet.

Man kann sich leicht vorstellen, dass moderne Rechner ein deutlich aufwendigeres und auf Geschwindigkeit optimierteres Bussystem besitzen. Im Zuge der Entwicklung wurden verschiedene Ansätze umgesetzt, denen allen gemein ist, dass sie nicht nur einen einzelnen Bus besitzen (wie die Von-Neumann-Architektur), sondern eine Reihe verschiedener Busse, die mit unterschiedlichen Geschwindigkeiten arbeiten.

Front Side Bus und Chipsatz mit North- sowie Southbridge

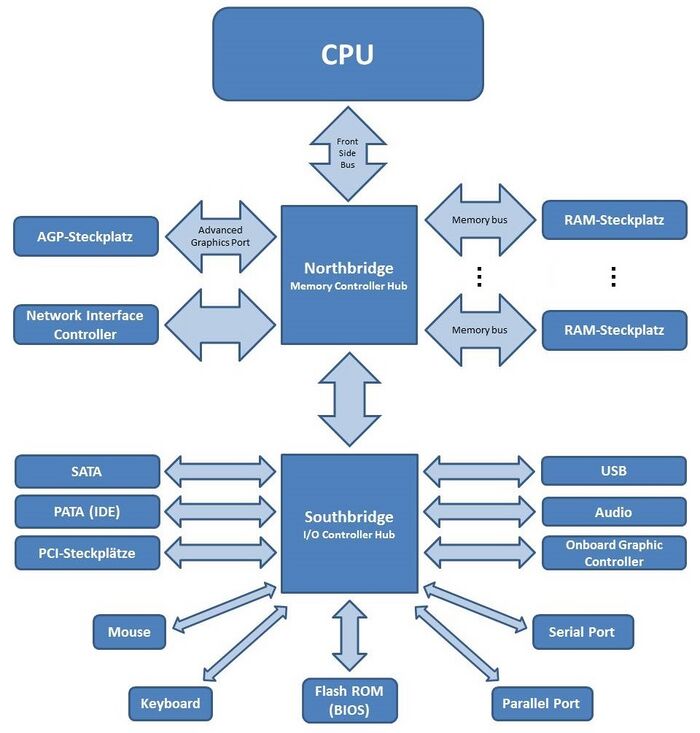

Boettcher 2006 zeigt in Kapitel 1.1.1, Abbildung 1.1, den Chipsatz, bestehend aus Northbridge und Southbridge, über den alle Komponenten eines Rechners über verschiedene Busse miteinander verbunden sind. Ein ähnlicher Aufbau ist bei Mandl 2013 in Kapitel 1.1, Abbildung 1-4, zu sehen.

Die CPU ist über den Front Side Bus mit der Northbridge verbunden. Diese bedient alle schnell arbeitenden Komponenten, wie Hauptspeicher, AGP-Grafikkarte und Gigabit-Ethernet-Karte. Weiterhin steht sie in Verbindung mit der Southbridge.

Die Southbridge bedient alle langsamer arbeitenden Komponenten. Sie ist der Knotenpunkt aller mit geringerer Geschwindigkeit arbeitenden Busse, an die z.B. Festplatten und CD/DVD-Laufwerke angeschlossen sind, ebenso gibt es Verbindungen zu den Peripheral-Component-Interconnect-Steckplätzen (kurz: PCI-Slots) und dem Universal-Serial-Bus mit seinen USB-Ports.

Die folgende Abbildung zeigt die North- und die Southbridge als zentrale Verbindungspunkte aller Komponenten.

QuickPath Interconnect statt Front Side Bus

Auf Wikipedia ist eine Abbildung des ASUS-Mainboards P6T Deluxe zu sehen. Die zugehörige Wiki-Seite benennt viele der auf dem Mainboard integrierten Komponenten, u.a. auch eine North- und Southbridge.

Asus selbst hat die Spezifikation dieser Hauptplatine ebenfalls im Internet bereitgestellt. Im Handbuch (downloadbar unter "Manual") wird Intel(R) QuickPath Interconnect (kurz: QPI) als Verbindung von der CPU zur Northbridge erwähnt. QPI hat damit den Front Side Bus abgelöst. Eine Einführung in QuickPath Interconnect stellt Intel zum Download bereit.

HyperTransport als Alternative zu QuickPath Interconnect

Eine Alternative zu QPI stellt HyperTransport (HT) dar. Es wurde (zeitlich noch vor QPI) als offener Standard von einem herstellerübergreifenden Konsortium, dem u.a. die Firmen Advanced Micro Devices (AMD), International Business Machines (IBM) und Apple angehören, entwickelt und standardisiert.

HyperTransport wurde eingeführt, um

- mehrere Prozessoren miteinander zu verbinden,

- Prozessoren mit Coprozessoren zu verbinden,

- Prozessoren mit sonstigen I/O-Komponenten (z.B. North- / Southbridge) zu verbinden.

Northbridge in die CPU integriert

Die Intel Corporation ist ein US-amerikanischer Halbleiterersteller und bekannt für die Produktion von (u.a.) CPUs und Chipsätzen. Eine Produktreihe aus 2012/13 zeigt hier beispielhaft die aktuelle Tendenz in der Weiterentwicklung der Bus-Technologien.

Intel(R) zeigt in Technical Product Specification, Server Board 2600GZ/GL in Kapitel 3 (Product Architecture Overview), Figure 9, den Aufbau einer Hauptplatine mit zwei CPUs. Beide Prozessoren sind miteinander über QuickPath-Interconnect (QPI) verbunden. Weiterhin haben sie eine direkte Anbindung an die Speicherbänke des Hauptspeichers.

Die erste CPU ist direkt mit dem Ethernet-Controller I350 verbunden. Im I350 Reference Design wird auf Seite 3 der Aufbau dieses Controllers gezeigt. Er verfügt über vier Ethernet-Ports (RJ45), PCIE-G2 ist die Verbindung zur CPU.

Eine separate Northbridge ist damit entfallen, ihre Funktionen wurden direkt in die CPU (Intel(R) Xeon(R) E5-2600) intergriert, was einen Geschwindigkeitsgewinn erwarten lässt.

Eine Southbridge ist mit dem Intel (R) C602 weiterhin vorhanden und stellt die erwarteten Verbindungen bereit.

Auf Abbildungen wurde an dieser Stelle aus Gründen des Copyrights bewusst verzichtet. Die oben im Text genannten Links führen aber direkt zu Dokumenten oder Webseiten, welche entsprechende Grafiken enthalten. Das eigenständige Abrufen der Abbildungen über die entsprechenden Links sei an dieser Stelle dem Leser überlassen.

Weiterführende Literatur

Huette 2012 zählen in Kapitel (J) 7.1.5 einige Bussysteme auf und geben jeweils in kompakter Form ergänzende Informationen dazu. Die Lektüre dieser Quelle sei empfohlen.

Studierende sind oftmals berechtigt, eine PDF-Version dieses Buches ohne entstehende Kosten über ihre Hochschulen von Springerlink zu beziehen.

IDE, SATA, USB & Co

Weiterführende Literatur

Huette 2012 zählen in Kapitel (J) 7.1.6 einige periphere Busse (u.a. IDE, USB) auf und geben jeweils in kompakter Form ergänzende Informationen dazu. Die Lektüre dieser Quelle sei empfohlen.

Studierende sind oftmals berechtigt, eine PDF-Version dieses Buches ohne entstehende Kosten über ihre Hochschulen von Springerlink zu beziehen.