2.3.5 DMA-Controller

| [gesichtete Version] | [gesichtete Version] |

(→Allgemeiner Ablauf: - ist Peripheriegerät gemeint? Betribsmittel kann auch ein Kuli sein....) |

(LOOP2 Upgrade) |

||

| Zeile 1: | Zeile 1: | ||

=DMA-Controller= | =DMA-Controller= | ||

<p> | <p> | ||

Ein <loop_index>DMA-Controller|Controller, DMA|Direct Memory Access|DMA</loop_index>'''DMA-Controller''' ist eine Hardware-Komponente, die zum Ziel hat, die Geschwindigkeit des Gesamtsystems zu erhöhen. Erreicht werden soll dies u.a. durch eine Reduzierung der Anzahl an Interrupts, die bei der Kommunikation zwischen der CPU und den E/A-Geräten ausgelöst werden. | Ein <loop_index id="5fa9784eaaeb0">DMA-Controller|Controller, DMA|Direct Memory Access|DMA</loop_index>'''DMA-Controller''' ist eine Hardware-Komponente, die zum Ziel hat, die Geschwindigkeit des Gesamtsystems zu erhöhen. Erreicht werden soll dies u.a. durch eine Reduzierung der Anzahl an Interrupts, die bei der Kommunikation zwischen der CPU und den E/A-Geräten ausgelöst werden. | ||

</p> | </p> | ||

| Zeile 7: | Zeile 7: | ||

== Wichtige Voraussetzung! == | == Wichtige Voraussetzung! == | ||

<p> | <p> | ||

<loop_index>enormer Aufwand ohne DMA</loop_index> | <loop_index id="5fa9784eaaebd">enormer Aufwand ohne DMA</loop_index> | ||

<loop_area type="important"> | <loop_area type="important"> | ||

<p> | <p> | ||

| Zeile 27: | Zeile 27: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Datentransfer (noch) ohne DMA"> | <loop_task title="Datentransfer (noch) ohne DMA" id="5fa9784eaaec7"> | ||

<p> | <p> | ||

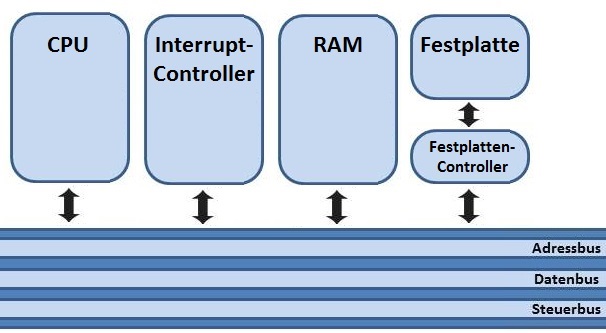

Erläutere anhand der folgenden (vereinfachten) Abbildung, wie der Transfer von Daten zwischen Festplatte und RAM abläuft. Wann treten dabei Interrupts auf? | Erläutere anhand der folgenden (vereinfachten) Abbildung, wie der Transfer von Daten zwischen Festplatte und RAM abläuft. Wann treten dabei Interrupts auf? | ||

</p> | </p> | ||

<p> | <p> | ||

<loop_figure title="Vereinfachter Rechner, noch ohne DMA-Controller" description="" copyright="CC-BY" index=true show_copyright=true> | <loop_figure title="Vereinfachter Rechner, noch ohne DMA-Controller" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9784eaaed2"> | ||

[[Datei:dma-ohne.jpg]] | [[Datei:dma-ohne.jpg]] | ||

</loop_figure> | </loop_figure> | ||

| Zeile 53: | Zeile 53: | ||

=== Allgemeiner Ablauf === | === Allgemeiner Ablauf === | ||

<p> | <p> | ||

Der allgemeine <loop_index>Ablauf, DMA|DMA, Ablauf|Arbeitsweise, DMA|DMA, Arbeitsweise</loop_index>Ablauf des DMA-Verfahrens ist wie folgt: | Der allgemeine <loop_index id="5fa9784eaaedc">Ablauf, DMA|DMA, Ablauf|Arbeitsweise, DMA|DMA, Arbeitsweise</loop_index>Ablauf des DMA-Verfahrens ist wie folgt: | ||

</p> | </p> | ||

| Zeile 89: | Zeile 89: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Datentransfer mit DMA"> | <loop_task title="Datentransfer mit DMA" id="5fa9784eaaee6"> | ||

<p> | <p> | ||

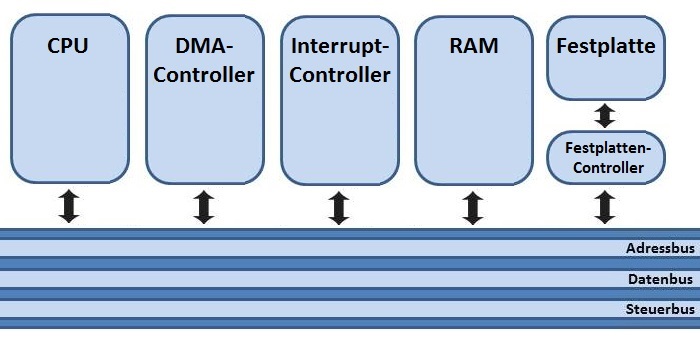

Erläutere anhand der folgenden (vereinfachten) Abbildung, wie der Transfer von Daten zwischen Festplatte und RAM abläuft, wenn ein DMA-Controller zur Verfügung steht. Wann und wie oft muss die CPU auf ein Interruptsignal reagieren? <small>(Gemeint sind nur die Interrupts, welche durch den Datentransfer ausgelöst werden.)</small> | Erläutere anhand der folgenden (vereinfachten) Abbildung, wie der Transfer von Daten zwischen Festplatte und RAM abläuft, wenn ein DMA-Controller zur Verfügung steht. Wann und wie oft muss die CPU auf ein Interruptsignal reagieren? <small>(Gemeint sind nur die Interrupts, welche durch den Datentransfer ausgelöst werden.)</small> | ||

| Zeile 97: | Zeile 97: | ||

</p> | </p> | ||

<p> | <p> | ||

<loop_figure title="Vereinfachter Rechner, mit DMA-Controller" description="" copyright="CC-BY" index=true show_copyright=true> | <loop_figure title="Vereinfachter Rechner, mit DMA-Controller" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9784eaaef1"> | ||

[[Datei:dma-mit.jpg]] | [[Datei:dma-mit.jpg]] | ||

</loop_figure> | </loop_figure> | ||

| Zeile 109: | Zeile 109: | ||

== Der DMA-Controller macht den Unterschied == | == Der DMA-Controller macht den Unterschied == | ||

<p> | <p> | ||

Die <loop_index>Einsparung von Interrupts|Interrupt, Einsparung</loop_index>Einsparung von Interrupts führt unweigerlich zu einer Beschleunigung des Gesamtsystems, da die Abarbeitung jedes einzelnen Interrupts sehr aufwendig ist. Der Abschnitt [http://vfhcab.oncampus.de/loop/Kommunikation_mit_E/A-Geräten#Datentransfer_und_Interrupts Datentransfer und Interrupts] hat dies bereits gezeigt. | Die <loop_index id="5fa9784eaaefb">Einsparung von Interrupts|Interrupt, Einsparung</loop_index>Einsparung von Interrupts führt unweigerlich zu einer Beschleunigung des Gesamtsystems, da die Abarbeitung jedes einzelnen Interrupts sehr aufwendig ist. Der Abschnitt [http://vfhcab.oncampus.de/loop/Kommunikation_mit_E/A-Geräten#Datentransfer_und_Interrupts Datentransfer und Interrupts] hat dies bereits gezeigt. | ||

</p> | </p> | ||

| Zeile 117: | Zeile 117: | ||

<p> | <p> | ||

<cite>Brinkschulte+et.al.+2010</cite> erläutern beispielsweise, dass eine Datenübertragung auf der CPU mittels einer in Software programmierten Schleife erfolgt, während auf einem spezialisierten DMA-Controller jegliche Steuerung mittels Hardware erfolgt. | <cite id="5fa9784eaaf06">Brinkschulte+et.al.+2010</cite> erläutern beispielsweise, dass eine Datenübertragung auf der CPU mittels einer in Software programmierten Schleife erfolgt, während auf einem spezialisierten DMA-Controller jegliche Steuerung mittels Hardware erfolgt. | ||

</p> | </p> | ||

| Zeile 124: | Zeile 124: | ||

<loop_area type="notice">'''Weiterführende Literatur''' | <loop_area type="notice">'''Weiterführende Literatur''' | ||

<p> | <p> | ||

<cite>Brinkschulte+et.al.+2010</cite> erläutern in Kapitel 4.6 (DMA) weitere Hintergründe zum Thema. Die Lektüre dieser Quelle sei ausdrücklich empfohlen.</p> | <cite id="5fa9784eaaf10">Brinkschulte+et.al.+2010</cite> erläutern in Kapitel 4.6 (DMA) weitere Hintergründe zum Thema. Die Lektüre dieser Quelle sei ausdrücklich empfohlen.</p> | ||

<p> | <p> | ||

<small>Studierende sind oftmals berechtigt, eine PDF-Version dieses Buches ohne entstehende Kosten [[Hinweise für Studierende#Downloadbare Bücher von Springerlink|über ihre Hochschulen von Springerlink zu beziehen.]]</small> | <small>Studierende sind oftmals berechtigt, eine PDF-Version dieses Buches ohne entstehende Kosten [[Hinweise für Studierende#Downloadbare Bücher von Springerlink|über ihre Hochschulen von Springerlink zu beziehen.]]</small> | ||

| Zeile 136: | Zeile 136: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="DMA und CPU"> | <loop_task title="DMA und CPU" id="5fa9784eaaf1a"> | ||

<p> | <p> | ||

Der Einsatz eines DMA-Controllers hat nicht nur Vorteile. Ein Nachteil ist beispielsweise, dass Datenbus und Adressbus während eines Datentransfers per DMA nicht der CPU zur Verfügung stehen. | Der Einsatz eines DMA-Controllers hat nicht nur Vorteile. Ein Nachteil ist beispielsweise, dass Datenbus und Adressbus während eines Datentransfers per DMA nicht der CPU zur Verfügung stehen. | ||

| Zeile 152: | Zeile 152: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Arten des DMA-Transfers"> | <loop_task title="Arten des DMA-Transfers" id="5fa9784eaaf25"> | ||

<p> | <p> | ||

<cite>Brinkschulte+et.al.+2010</cite> beschreiben in Kapitel 4.6 drei Arten des DMA-Transfers. | <cite id="5fa9784eaaf30">Brinkschulte+et.al.+2010</cite> beschreiben in Kapitel 4.6 drei Arten des DMA-Transfers. | ||

</p> | </p> | ||

<p> | <p> | ||

Version vom 9. November 2020, 19:11 Uhr

DMA-Controller

Ein DMA-Controller ist eine Hardware-Komponente, die zum Ziel hat, die Geschwindigkeit des Gesamtsystems zu erhöhen. Erreicht werden soll dies u.a. durch eine Reduzierung der Anzahl an Interrupts, die bei der Kommunikation zwischen der CPU und den E/A-Geräten ausgelöst werden.

Wichtige Voraussetzung!

Du erinnerst dich doch noch an den enormen Aufwand, der betrieben wurde, um ein einzelnes Datenwort von der Festplatte, über die CPU in den Hauptspeicher zu kopieren, oder?

Und daran, dass für jedes einzelne Datenwort ein Interrupt ausgelöst wurde, oder?

Falls nicht: Lies dir erst das Kapitel Kommunikation mit E/A-Geräten noch einmal durch, und schau dir das Video an!

Mit der Bearbeitung der folgenden Aufgabe 1 reflektierst du noch einmal diesen wichtigen Sachverhalt.

Aufgabe 1

Erläutere anhand der folgenden (vereinfachten) Abbildung, wie der Transfer von Daten zwischen Festplatte und RAM abläuft. Wann treten dabei Interrupts auf?

Direct Memory Access

Die Abkürzung DMA steht für Direct Memory Access, auf Deutsch also: direkter Speicherzugriff, und beschreibt die Möglichkeit, Datenwörter direkt zwischen dem Hauptspeicher und einem DMA-fähigen Peripheriegerät auszutauschen, ohne dass daran die CPU beteiligt ist.

Die CPU wird also durch einen vorhandenen DMA-Controller entlastet. Sie muss lediglich zu Beginn und am Ende der Übertragung eingreifen.

Allgemeiner Ablauf

Der allgemeine Ablauf des DMA-Verfahrens ist wie folgt:

- Daten sollen zwischen dem Hauptspeicher und einem weiteren DMA-fähigen Peripheriegerät übertragen werden.

- Die CPU versorgt den DMA-Controller mit allen notwendigen Informationen:

Beteiligte Komponenten

Start- und Zieladresse

Anzahl zu übertragener Datenwörter

Übertragungsrichtung - Die CPU erteilt dem DMA-Controller die Erlaubnis, mit der Datenübertragung zu beginnen.

- Der DMA-Controller steuert die Übertragung aller Datenwörter zwischen den beteiligten Betriebsmitteln. Die Übertragung geschieht über das Bus-System.

- Sobald alle Daten übertragen sind, informiert der DMA-Controller mit einem Interrupt über den Abschluss des Datentransfers.

- Der Interrupt-Controller empfängt den Interrupt und leitet ihn an die CPU weiter.

- Auf der CPU wird die zugehörige Interruptbehandlungsroutine ausgeführt.

- Die Datenübertragung per DMA ist abgeschlossen.

Reduzierung der Anzahl der Interrupts

An der vorangegangenen Auflistung ist erkennbar, dass bei Einsatz des DMA-Controllers die Anzahl der Interrupts deutlich reduziert wird. Die CPU muss somit sehr viel weniger Interruptbehandlungsroutinen ausführen, die so gewonnene CPU-Zeit kommt anderen Prozessen zu Gute.

Bei einem Datentransfer ohne DMA-Controller ereignete sich ein Interrupt pro Datenwort.

Mit DMA-Controller ist es nur noch ein Interrupt für die gesamte Übertragung.

Aufgabe 2

Erläutere anhand der folgenden (vereinfachten) Abbildung, wie der Transfer von Daten zwischen Festplatte und RAM abläuft, wenn ein DMA-Controller zur Verfügung steht. Wann und wie oft muss die CPU auf ein Interruptsignal reagieren? (Gemeint sind nur die Interrupts, welche durch den Datentransfer ausgelöst werden.)

Welche Änderungen ergeben sich zu Aufgabe 1 oben?

Der DMA-Controller macht den Unterschied

Die Einsparung von Interrupts führt unweigerlich zu einer Beschleunigung des Gesamtsystems, da die Abarbeitung jedes einzelnen Interrupts sehr aufwendig ist. Der Abschnitt Datentransfer und Interrupts hat dies bereits gezeigt.

Ein weiterer Grund für einen Geschwindigkeitsvorteil ist, dass ein DMA-Controller von seiner Bauart her auf Datenübertragungen spezialisiert ist. Er kann diese Tätigkeiten deshalb mit einer höheren Geschwindigkeit ausführen, als eine CPU, die universell für viele verschiedene Tätigkeiten entwickelt wurde.

erläutern beispielsweise, dass eine Datenübertragung auf der CPU mittels einer in Software programmierten Schleife erfolgt, während auf einem spezialisierten DMA-Controller jegliche Steuerung mittels Hardware erfolgt.

Weiterführende Literatur

erläutern in Kapitel 4.6 (DMA) weitere Hintergründe zum Thema. Die Lektüre dieser Quelle sei ausdrücklich empfohlen.

Studierende sind oftmals berechtigt, eine PDF-Version dieses Buches ohne entstehende Kosten über ihre Hochschulen von Springerlink zu beziehen.

Aufgabe 3

Der Einsatz eines DMA-Controllers hat nicht nur Vorteile. Ein Nachteil ist beispielsweise, dass Datenbus und Adressbus während eines Datentransfers per DMA nicht der CPU zur Verfügung stehen.

- Welche Auswirkungen hat dies auf die Arbeitsweise der CPU?

- Was kann die CPU während der Zeit des DMA-Transfers erledigen, und was geht nicht mehr?

Aufgabe 4

beschreiben in Kapitel 4.6 drei Arten des DMA-Transfers.

- Welche drei Arten werden beschrieben?

- Worin unterscheiden sie sich?

- Welche Auswirkungen hat dies auf die Arbeit der CPU?

- Bei einer der beschriebenen Arten hat das beteiligte E/A-Gerät die Möglichkeit zu bestimmen, wann der Bus für den DMA-Transfer reserviert wird.

Erläutere, warum dies Sinn macht!

Berücksichtige dabei die unterschiedlichen Geschwindigkeiten, mit denen Hauptspeicher und E/A-Geräte arbeiten.