2.3.4 Interrupt-Controller

| [gesichtete Version] | [gesichtete Version] |

(LOOP2 Upgrade) |

|||

| Zeile 1: | Zeile 1: | ||

=Interrupt-Controller= | =Interrupt-Controller= | ||

<p> | <p> | ||

Der <loop_index>Interrupt|Interrupt-Controller|Controller, Interrupt</loop_index>'''Interrupt-Controller''' ist ein weiterer Hardware-Baustein in der Architektur eines Computers. Seine Aufgabe besteht darin, Interrupt-Signale von verschiedenen Komponenten des Rechners entgegen zu nehmen, und die CPU über das Vorliegen von einem (oder mehreren) Interrupts zu informieren. | Der <loop_index id="5fa97861a7878">Interrupt|Interrupt-Controller|Controller, Interrupt</loop_index>'''Interrupt-Controller''' ist ein weiterer Hardware-Baustein in der Architektur eines Computers. Seine Aufgabe besteht darin, Interrupt-Signale von verschiedenen Komponenten des Rechners entgegen zu nehmen, und die CPU über das Vorliegen von einem (oder mehreren) Interrupts zu informieren. | ||

</p> | </p> | ||

<p> | <p> | ||

Die CPU ist dann für die Abarbeitung des Interrupts zuständig. Dies geschieht, indem eine sogenannte <loop_index>Interruptbehandlungsroutine</loop_index>Interruptbehandlungsroutine aufgerufen wird. | Die CPU ist dann für die Abarbeitung des Interrupts zuständig. Dies geschieht, indem eine sogenannte <loop_index id="5fa97861a7883">Interruptbehandlungsroutine</loop_index>Interruptbehandlungsroutine aufgerufen wird. | ||

</p> | </p> | ||

| Zeile 10: | Zeile 10: | ||

== Definition: Interruptbehandlungsroutine == | == Definition: Interruptbehandlungsroutine == | ||

<p> | <p> | ||

<loop_index>ISR, Interrupt Service Routine|Interrupt Service Routine</loop_index> | <loop_index id="5fa97861a788c">ISR, Interrupt Service Routine|Interrupt Service Routine</loop_index> | ||

<loop_area type="definition"> | <loop_area type="definition"> | ||

<p> | <p> | ||

| Zeile 22: | Zeile 22: | ||

== Interrupt bedeutet Unterbrechung == | == Interrupt bedeutet Unterbrechung == | ||

<p> | <p> | ||

Die deutsche Übersetzung des englischen Begriffs "Interrupt" ist "<loop_index>Unterbrechung, Interrupt</loop_index>Unterbrechung". Und genau diese Unterbrechung eines laufenden Prozesses passiert in dem Moment, in dem sich die CPU entschließt, einen vom Interrupt-Controller angezeigten Interrupt zu bearbeiten. | Die deutsche Übersetzung des englischen Begriffs "Interrupt" ist "<loop_index id="5fa97861a7894">Unterbrechung, Interrupt</loop_index>Unterbrechung". Und genau diese Unterbrechung eines laufenden Prozesses passiert in dem Moment, in dem sich die CPU entschließt, einen vom Interrupt-Controller angezeigten Interrupt zu bearbeiten. | ||

</p> | </p> | ||

<p> | <p> | ||

| Zeile 29: | Zeile 29: | ||

<p> | <p> | ||

<loop_area icon="Video.png" icontext="Video"> | <loop_area icon="Video.png" icontext="Video"> | ||

<loop_media type="video" title="Interrupt-Controller (01:30)" description="http://youtu.be/ML9mwQ5TyzI" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|ML9mwQ5TyzI|700}}</loop_media> | <loop_media type="video" title="Interrupt-Controller (01:30)" description="http://youtu.be/ML9mwQ5TyzI" copyright="CC-BY" index=true show_copyright=true id="5fa97861a789d">{{#ev:youtube|ML9mwQ5TyzI|700}}</loop_media> | ||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

<br /> | <br /> | ||

<p> | <p> | ||

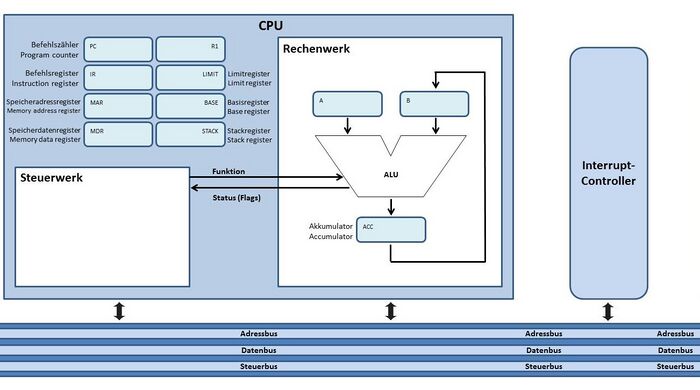

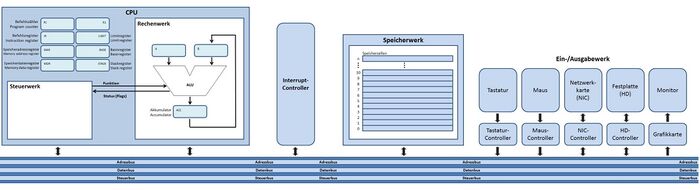

Im Video ist erkennbar, dass der Interrupt-Controller als eigenständige Hardware-Komponente über den <loop_index>Systembus</loop_index>Systembus mit anderen Komponenten und insbesondere mit der CPU kommuniziert. | Im Video ist erkennbar, dass der Interrupt-Controller als eigenständige Hardware-Komponente über den <loop_index id="5fa97861a78a5">Systembus</loop_index>Systembus mit anderen Komponenten und insbesondere mit der CPU kommuniziert. | ||

</p> | </p> | ||

<br /> | <br /> | ||

<p> | <p> | ||

<loop_figure title="CPU mit Interrupt-Controller" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Cpu13-interrupt-controller.jpg|700px]]</loop_figure> | <loop_figure title="CPU mit Interrupt-Controller" description="" copyright="CC-BY" index=true show_copyright=true id="5fa97861a78ad">[[Datei:Cpu13-interrupt-controller.jpg|700px]]</loop_figure> | ||

</p> | </p> | ||

<br /> | <br /> | ||

<p> | <p> | ||

<loop_figure title="Interrupt-Controller im Gesamtbild" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:vnrgesamt2.jpg|700px]]</loop_figure> | <loop_figure title="Interrupt-Controller im Gesamtbild" description="" copyright="CC-BY" index=true show_copyright=true id="5fa97861a78b5">[[Datei:vnrgesamt2.jpg|700px]]</loop_figure> | ||

</p> | </p> | ||

| Zeile 49: | Zeile 49: | ||

<loop_area type="notice">'''Weiterführende Literatur''' | <loop_area type="notice">'''Weiterführende Literatur''' | ||

<p> | <p> | ||

<cite>Wüst+2011</cite> erläutert in den Kapiteln 8.1 (Interrupts) und 8.2 (Ausnahmen) weitere Hintergründe zu den genannten Themen. Die Lektüre dieser Quelle sei ausdrücklich empfohlen. | <cite id="5fa97861a78bd">Wüst+2011</cite> erläutert in den Kapiteln 8.1 (Interrupts) und 8.2 (Ausnahmen) weitere Hintergründe zu den genannten Themen. Die Lektüre dieser Quelle sei ausdrücklich empfohlen. | ||

</p> | </p> | ||

<p> | <p> | ||

| Zeile 61: | Zeile 61: | ||

<loop_area type="notice">'''Weiterführende Literatur''' | <loop_area type="notice">'''Weiterführende Literatur''' | ||

<p> | <p> | ||

<cite>Mandl+2013</cite> erläutert in Kapitel 3.1 (Interrupts) weitere Hintergründe zum Thema. Die Lektüre dieser Quelle sei ausdrücklich empfohlen. | <cite id="5fa97861a78c6">Mandl+2013</cite> erläutert in Kapitel 3.1 (Interrupts) weitere Hintergründe zum Thema. Die Lektüre dieser Quelle sei ausdrücklich empfohlen. | ||

</p> | </p> | ||

<p> | <p> | ||

| Zeile 78: | Zeile 78: | ||

== Keine negative Beeinträchtigung == | == Keine negative Beeinträchtigung == | ||

<p> | <p> | ||

Ein entscheidendes Kriterium bei der Abarbeitung eines Interrupts durch die CPU ist, dass der durch den Interrupt unterbrochene Prozess später '''ohne negative Beeinträchtigung''' weiter ausgeführt werden kann. Das vom Prozess erarbeitete Ergebnis darf sich nicht unterscheiden, egal, ob während der Abarbeitung ein (oder mehrere) Interrupt(s) aufträt(en), oder nicht. Erreicht wird dieses durch die Einhaltung der Bedingungen einer <loop_index>präzise Unterbrechung|präzise Unterbrechung, Bedingungen|Bedingungen präzise Unterbrechung|Unterbrechung, präzise|Precise interrupt|Interrupt, precise</loop_index>präzisen Unterbrechung. | Ein entscheidendes Kriterium bei der Abarbeitung eines Interrupts durch die CPU ist, dass der durch den Interrupt unterbrochene Prozess später '''ohne negative Beeinträchtigung''' weiter ausgeführt werden kann. Das vom Prozess erarbeitete Ergebnis darf sich nicht unterscheiden, egal, ob während der Abarbeitung ein (oder mehrere) Interrupt(s) aufträt(en), oder nicht. Erreicht wird dieses durch die Einhaltung der Bedingungen einer <loop_index id="5fa97861a78ce">präzise Unterbrechung|präzise Unterbrechung, Bedingungen|Bedingungen präzise Unterbrechung|Unterbrechung, präzise|Precise interrupt|Interrupt, precise</loop_index>präzisen Unterbrechung. | ||

</p> | </p> | ||

| Zeile 100: | Zeile 100: | ||

== Definition: Unpräzise Unterbrechung == | == Definition: Unpräzise Unterbrechung == | ||

<p> | <p> | ||

<loop_index>Unpräzise Unterbrechung|Unterbrechung, unpräzise|Imprecise interrupt|Interrupt, imprecise</loop_index> | <loop_index id="5fa97861a78d5">Unpräzise Unterbrechung|Unterbrechung, unpräzise|Imprecise interrupt|Interrupt, imprecise</loop_index> | ||

<loop_area type="definition"> | <loop_area type="definition"> | ||

<p> | <p> | ||

| Zeile 114: | Zeile 114: | ||

<p> | <p> | ||

<loop_area icon="Video.png" icontext="Video"> | <loop_area icon="Video.png" icontext="Video"> | ||

<loop_media type="video" title="Was passiert bei einem Interrupt? (02:14)" description="http://youtu.be/_wVNpUW3kdM" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|_wVNpUW3kdM|700}}</loop_media> | <loop_media type="video" title="Was passiert bei einem Interrupt? (02:14)" description="http://youtu.be/_wVNpUW3kdM" copyright="CC-BY" index=true show_copyright=true id="5fa97861a78dd">{{#ev:youtube|_wVNpUW3kdM|700}}</loop_media> | ||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

| Zeile 127: | Zeile 127: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Prüfe die Bedingungen!"> | <loop_task title="Prüfe die Bedingungen!" id="5fa97861a78e5"> | ||

<p> | <p> | ||

Prüfe anhand des [http://youtu.be/_wVNpUW3kdM Videos] für jede der [[Interrupt-Controller#Definition:_Präzise_Unterbrechung|vier Bedingungen einer präzisen Unterbrechung]], ob diese '''tatsächlich erfüllt''' ist! | Prüfe anhand des [http://youtu.be/_wVNpUW3kdM Videos] für jede der [[Interrupt-Controller#Definition:_Präzise_Unterbrechung|vier Bedingungen einer präzisen Unterbrechung]], ob diese '''tatsächlich erfüllt''' ist! | ||

| Zeile 144: | Zeile 144: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Schätze die Folgen ab!"> | <loop_task title="Schätze die Folgen ab!" id="5fa97861a78ed"> | ||

<p> | <p> | ||

Beschreibe ein Szenario, bei dem jeweils eine der [[Interrupt-Controller#Definition:_Präzise_Unterbrechung|vier Bedingungen einer präzisen Unterbrechung]] '''nicht erfüllt''' ist. | Beschreibe ein Szenario, bei dem jeweils eine der [[Interrupt-Controller#Definition:_Präzise_Unterbrechung|vier Bedingungen einer präzisen Unterbrechung]] '''nicht erfüllt''' ist. | ||

| Zeile 161: | Zeile 161: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Wer wenn nicht das Steuerwerk?"> | <loop_task title="Wer wenn nicht das Steuerwerk?" id="5fa97861a78f5"> | ||

<p> | <p> | ||

Im [http://youtu.be/_wVNpUW3kdM Video] wird gezeigt, wie der aktuelle Wert des Befehlszählers bei einer Unterbrechung in einem anderen Register gesichert wird. Alle weiteren Register oder die Statusflags werden hingegen nicht gesichert. | Im [http://youtu.be/_wVNpUW3kdM Video] wird gezeigt, wie der aktuelle Wert des Befehlszählers bei einer Unterbrechung in einem anderen Register gesichert wird. Alle weiteren Register oder die Statusflags werden hingegen nicht gesichert. | ||

| Zeile 176: | Zeile 176: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Vier Bit"> | <loop_task title="Vier Bit" id="5fa97861a78fd"> | ||

<p> | <p> | ||

Im [http://youtu.be/_wVNpUW3kdM Video] werden in den Registern PC und IR jeweils Werte abgelegt, die aus vier Bit bestehen. | Im [http://youtu.be/_wVNpUW3kdM Video] werden in den Registern PC und IR jeweils Werte abgelegt, die aus vier Bit bestehen. | ||

Version vom 9. November 2020, 19:12 Uhr

Interrupt-Controller

Der Interrupt-Controller ist ein weiterer Hardware-Baustein in der Architektur eines Computers. Seine Aufgabe besteht darin, Interrupt-Signale von verschiedenen Komponenten des Rechners entgegen zu nehmen, und die CPU über das Vorliegen von einem (oder mehreren) Interrupts zu informieren.

Die CPU ist dann für die Abarbeitung des Interrupts zuständig. Dies geschieht, indem eine sogenannte Interruptbehandlungsroutine aufgerufen wird.

Definition: Interruptbehandlungsroutine

Unter einer Interruptbehandlungsroutine (ISR, Interrupt Service Routine) versteht man eine Reihe von Anweisungen, die einem bestimmten Interrupt zugeordnet ist und deren Anweisungen auf einer CPU ausgeführt werden können.

Interrupt bedeutet Unterbrechung

Die deutsche Übersetzung des englischen Begriffs "Interrupt" ist "Unterbrechung". Und genau diese Unterbrechung eines laufenden Prozesses passiert in dem Moment, in dem sich die CPU entschließt, einen vom Interrupt-Controller angezeigten Interrupt zu bearbeiten.

Den vereinfachten Ablauf zeigt das folgende Video:

Im Video ist erkennbar, dass der Interrupt-Controller als eigenständige Hardware-Komponente über den Systembus mit anderen Komponenten und insbesondere mit der CPU kommuniziert.

Weiterführende Literatur

erläutert in den Kapiteln 8.1 (Interrupts) und 8.2 (Ausnahmen) weitere Hintergründe zu den genannten Themen. Die Lektüre dieser Quelle sei ausdrücklich empfohlen.

Studierende sind oftmals berechtigt, eine PDF-Version dieses Buches ohne entstehende Kosten über ihre Hochschulen von Springerlink zu beziehen.

Weiterführende Literatur

Mandl 2013 erläutert in Kapitel 3.1 (Interrupts) weitere Hintergründe zum Thema. Die Lektüre dieser Quelle sei ausdrücklich empfohlen.

Studierende sind oftmals berechtigt, eine PDF-Version dieses Buches ohne entstehende Kosten über ihre Hochschulen von Springerlink zu beziehen.

Es ist an dieser Stelle wichtig zu verstehen was genau passiert, wenn ein Interrupt auftritt und von der CPU bearbeitet wird. Die Beschreibung oben auf dieser Seite ist noch recht allgemein gehalten, weshalb jetzt einige entscheidende Details betrachtet werden sollen.

Keine negative Beeinträchtigung

Ein entscheidendes Kriterium bei der Abarbeitung eines Interrupts durch die CPU ist, dass der durch den Interrupt unterbrochene Prozess später ohne negative Beeinträchtigung weiter ausgeführt werden kann. Das vom Prozess erarbeitete Ergebnis darf sich nicht unterscheiden, egal, ob während der Abarbeitung ein (oder mehrere) Interrupt(s) aufträt(en), oder nicht. Erreicht wird dieses durch die Einhaltung der Bedingungen einer präzisen Unterbrechung.

Definition: Präzise Unterbrechung

Einen Interrupt nennt man eine präzise Unterbrechung (precise interrupt), falls alle der folgenden Bedingungen erfüllt sind:

- Der Programmzähler des unterbrochenen Prozesses wird an einer bekannten Stelle gesichert.

- Alle Befehle des unterbrochenen Prozesses, die vor dem Befehl ausgeführt werden müssen, auf den der Programmzähler zeigt, sind vollständig abgearbeitet.

- Kein Befehl des unterbrochenen Prozesses, der nach dem Befehl ausgeführt werden muss, auf den der Programmzähler zeigt, ist bereits abgearbeitet.

- Der Ausführungszustand des Befehls des unterbrochenen Prozesses, auf den der Programmzähler zeigt, ist bekannt.

Definition: Unpräzise Unterbrechung

Einen Interrupt nennt man eine unpräzise Unterbrechung (Imprecise interrupt), falls mindestens eine der für einen präzisen Interrupt genannten Bedingungen nicht erfüllt ist.

Was bei einem Interrupt passiert

Das folgende Video zeigt ein Beispiel, anhand dessen nachvollzogen werden kann, was genau bei einem Interrupt passiert, und ob die Bedingungen für eine präzise Unterbrechung erfüllt werden.

Mit Hilfe dieses Videos ist es nun möglich, die folgenden Aufgaben zu bearbeiten:

Aufgabe 1

Prüfe anhand des Videos für jede der vier Bedingungen einer präzisen Unterbrechung, ob diese tatsächlich erfüllt ist!

- Ist Bedingung 1 erfüllt? Erläutere warum!

- Ist Bedingung 2 erfüllt? Erläutere warum!

- Ist Bedingung 3 erfüllt? Erläutere warum!

- Ist Bedingung 4 erfüllt? Erläutere warum!

Aufgabe 2

Beschreibe ein Szenario, bei dem jeweils eine der vier Bedingungen einer präzisen Unterbrechung nicht erfüllt ist.

- Was sind die Folgen, wenn Bedingung 1 nicht erfüllt ist?

- Was sind die Folgen, wenn Bedingung 2 nicht erfüllt ist?

- Was sind die Folgen, wenn Bedingung 3 nicht erfüllt ist?

- Was sind die Folgen, wenn Bedingung 4 nicht erfüllt ist?

Aufgabe 3

Im Video wird gezeigt, wie der aktuelle Wert des Befehlszählers bei einer Unterbrechung in einem anderen Register gesichert wird. Alle weiteren Register oder die Statusflags werden hingegen nicht gesichert.

- Wenn das Steuerwerk nicht für die Sicherung dieser Werte zuständig ist, wer oder was ist es dann?

(Auf verschiedenen anderen Seiten dieses Moduls ist die Antwort auf Wer-oder-was-Fragen stets "Das Betriebssystem", aber diese Antwort ist an dieser Stelle nicht zugelassen, sie ist viel zu allgemein.) - Wo können diese Werte gesichert werden?

- Welche Vor- und/oder Nachteile hat diese Verfahrensweise?

Aufgabe 4

Im Video werden in den Registern PC und IR jeweils Werte abgelegt, die aus vier Bit bestehen.

- Wie realistisch sind diese vier Bit?

- Wieviele Bit erwartest du hier bei deinem eigenen PC oder Laptop?