2.1.3.1.1 Steuerwerk / Leitwerk

| [gesichtete Version] | [gesichtete Version] |

Keine Bearbeitungszusammenfassung |

Kwastg (Diskussion | Beiträge) Keine Bearbeitungszusammenfassung |

||

| (25 dazwischenliegende Versionen von 7 Benutzern werden nicht angezeigt) | |||

| Zeile 1: | Zeile 1: | ||

<p> | |||

Eines der Bestandteile der CPU ist das Steuerwerk: | |||

</p> | |||

<br /> | |||

== Definition: Steuerwerk == | |||

<p> | <p> | ||

<loop_area type="definition"> | <loop_index id="5fa978806e482">Steuerwerk|Leitwerk</loop_index> | ||

<loop_area type="definition"> | |||

<p> | <p> | ||

Das '''Steuerwerk''' (oder '''Leitwerk''') ist ein Bestandteil der CPU und für die sequentielle Abarbeitung des im Speicherwerk befindlichen Programms zuständig. | Das '''Steuerwerk''' (oder '''Leitwerk''') ist ein Bestandteil der CPU und für die sequentielle Abarbeitung des im Speicherwerk befindlichen Programms zuständig. | ||

</p> | </p> | ||

| Zeile 9: | Zeile 16: | ||

<p> | <p> | ||

Damit ist sofort ersichtlich, dass eine Verbindung zwischen Steuerwerk und Speicherwerk | Damit ist sofort ersichtlich, dass eine Verbindung zwischen Steuerwerk und Speicherwerk existieren muss, damit das abzuarbeitende Programm, bzw. dessen einzelnen Anweisungen, vom Speicherwerk in das Steuerwerk übertragen werden können. | ||

</p> | </p> | ||

<br /> | |||

== Definition: Arbeitsweise des Steuerwerks == | |||

<p> | <p> | ||

<loop_area type="definition"> | <loop_area type="definition"> | ||

<p> | <p> | ||

Das Steuerwerk sendet die Adresse des aktuellen Befehls an das Speicherwerk und erhält von diesem als Antwort genau jenen Befehl, der an der übermittelten Adresse innerhalb des Speicherwerks steht. Sobald das Steuerwerk den Befehl erhalten hat, wird dieser ausgeführt. | Das Steuerwerk sendet die Adresse des aktuellen Befehls an das Speicherwerk und erhält von diesem als Antwort genau jenen Befehl, der an der übermittelten Adresse innerhalb des Speicherwerks steht. Sobald das Steuerwerk den Befehl erhalten hat, wird dieser ausgeführt. | ||

| Zeile 24: | Zeile 29: | ||

</p> | </p> | ||

<br /> | |||

== Einfache Sicht auf die Arbeitsweise des Steuerwerks == | |||

<p> | <p> | ||

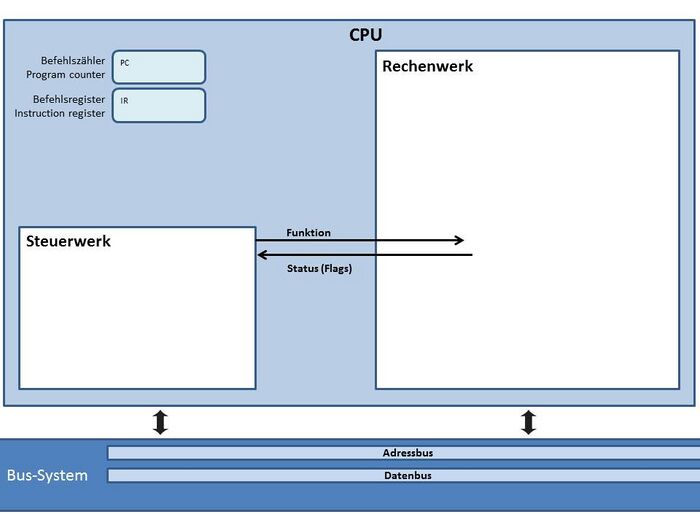

Es ergibt sich damit für die Arbeitsweise des Steuerwerks ein Kreislauf, der immer wieder durchlaufen wird: | Es ergibt sich damit für die Arbeitsweise des Steuerwerks ein Kreislauf, der immer wieder durchlaufen wird: | ||

| Zeile 29: | Zeile 36: | ||

<p> | <p> | ||

<loop_figure title="Eine einfache Sicht auf die Arbeitsweise des Steuerwerks" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Steuerwerk01.jpg|700px]]</loop_figure> | <loop_figure title="Eine einfache Sicht auf die Arbeitsweise des Steuerwerks" description="" copyright="CC-BY" index=true show_copyright=true id="5fa978806e491">[[Datei:Steuerwerk01.jpg|700px]]</loop_figure> | ||

</p> | </p> | ||

| Zeile 36: | Zeile 43: | ||

</p> | </p> | ||

<br /> | |||

<div class="clearer"></div> | |||

== Bestandteile der CPU == | |||

<p> | <p> | ||

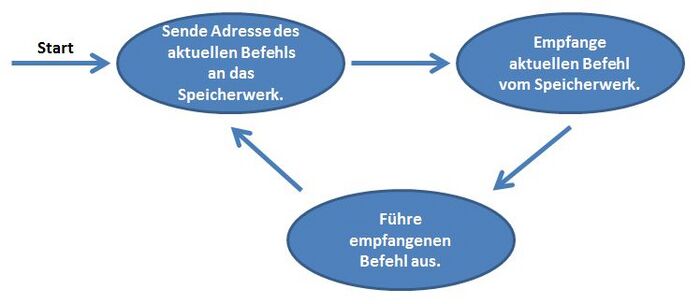

Aus der einfachen Sicht der Arbeitsweise des Steuerwerks lassen sich einige Bestandteile der CPU ableiten: | Aus der einfachen Sicht der Arbeitsweise des Steuerwerks lassen sich einige Bestandteile der CPU ableiten: | ||

<loop_index id="5fa978806e49b">Befehlszähler|PC, Befehlszähler|Program counter|PC, Program Counter|Befehlsregister|IR, Befehlsregister|Instruction Register|IR, Instruction Register</loop_index> | |||

* Damit die Adresse des aktuellen Befehls vom Steuerwerk verwaltet werden kann, muss es einen Speicherbereich dafür geben. Verwendet wird dazu ein Register, der sogenannte '''Befehlszähler''', engl. '''Program Counter''', kurz: '''PC'''. | * Damit die Adresse des aktuellen Befehls vom Steuerwerk verwaltet werden kann, muss es einen Speicherbereich dafür geben. Verwendet wird dazu ein Register, der sogenannte '''Befehlszähler''', engl. '''Program Counter''', kurz: '''PC'''. | ||

* Damit der vom Speicherwerk empfangene Befehl verwaltet werden kann, muss es einen Speicherbereich dafür geben. Verwendet wird dazu ein Register, das sogenannte '''Befehlsregister''', engl. '''Instruction Register''', kurz: '''IR'''. | * Damit der vom Speicherwerk empfangene Befehl verwaltet werden kann, muss es einen Speicherbereich dafür geben. Verwendet wird dazu ein Register, das sogenannte '''Befehlsregister''', engl. '''Instruction Register''', kurz: '''IR'''. | ||

| Zeile 44: | Zeile 54: | ||

</p> | </p> | ||

<br /> | |||

== Erweitertes Bild der CPU == | |||

<p> | <p> | ||

Man erhält ein leicht erweitertes Bild der CPU: | Man erhält ein leicht erweitertes Bild der CPU: | ||

| Zeile 49: | Zeile 61: | ||

<p> | <p> | ||

<loop_figure title="Steuerwerk mit Befehlszähler und Befehlsregister" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Cpu2.jpg|700px]]</loop_figure> | <loop_figure title="Steuerwerk mit Befehlszähler und Befehlsregister" description="" copyright="CC-BY" index=true show_copyright=true id="5fa978806e4a5">[[Datei:Cpu2.jpg|700px]]</loop_figure> | ||

</p> | </p> | ||

<br /> | |||

== Zusammenspiel PC, IR und Bus == | |||

<p> | <p> | ||

Das folgende Video geht näher auf das Zusammenspiel von Befehlszähler (PC) und Befehlsregister (IR) mit dem Bus-System ein. Die Fachbegriffe '''Adressbus''' und '''Datenbus''' werden eingeführt und erläutert. | Das folgende Video geht näher auf das Zusammenspiel von Befehlszähler (PC) und Befehlsregister (IR) mit dem Bus-System ein. Die Fachbegriffe '''Adressbus''' und '''Datenbus''' werden eingeführt und erläutert. | ||

| Zeile 57: | Zeile 71: | ||

<p> | <p> | ||

<loop_media type="video" title="Befehlszähler und Befehlsregister im Zusammenspiel mit dem Bus-System (03:07)" description="http://youtu.be/2IxOCLy5jms" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|2IxOCLy5jms}}</loop_media> | <loop_area icon="Video.png" icontext="Video"> | ||

<loop_media type="video" title="Befehlszähler und Befehlsregister im Zusammenspiel mit dem Bus-System (03:07)" description="http://youtu.be/2IxOCLy5jms" copyright="CC-BY" index=true show_copyright=true id="5fa978806e4b0">{{#ev:youtube|2IxOCLy5jms|700}}</loop_media> | |||

</loop_area> | |||

</p> | </p> | ||

<br /> | |||

<p> | <p> | ||

Zu den Erläuterungen im Video folgen hier noch einige Definitionen. | Zu den Erläuterungen im Video folgen hier noch einige Definitionen. | ||

</p> | </p> | ||

<br /> | |||

== Definition: (Paralleler) Bus == | |||

<p> | <p> | ||

<loop_area type="definition"> | <loop_index id="5fa978806e4b9">Bus, Paralleler Bus|Binary Unit System|Paralleler Bus</loop_index> | ||

<loop_area type="definition"> | |||

<p> | <p> | ||

Ein '''Bus''' ('''Binary Unit System''') dient zur parallelen Übertragung einer Gruppe von Bits. | Ein '''Bus''' ('''Binary Unit System''') dient zur parallelen Übertragung einer Gruppe von Bits. | ||

</p> | </p> | ||

| Zeile 77: | Zeile 96: | ||

<p> | <p> | ||

Es können mehrere Komponenten an einem Bus angeschlossen sein, so dass sich Quelle und Ziel der übertragenen Bits benennen lassen. | Es können mehrere Komponenten an einem Bus angeschlossen sein, so dass sich '''Quelle''' und '''Ziel''' der übertragenen Bits benennen lassen. | ||

</p> | </p> | ||

<br /> | |||

== Definition: Busbreite == | |||

<p> | <p> | ||

<loop_area type="definition"> | <loop_index id="5fa978806e4c3">Busbreite|Breite, Bus</loop_index> | ||

<loop_area type="definition"> | |||

<p> | <p> | ||

Die Anzahl der parallel übertragbaren Bits auf einem Bus nennt man die '''Breite des Busses''' oder '''Busbreite'''. | Die Anzahl der parallel übertragbaren Bits auf einem Bus nennt man die '''Breite des Busses''' oder '''Busbreite'''. | ||

</p> | </p> | ||

| Zeile 93: | Zeile 114: | ||

</p> | </p> | ||

<br /> | |||

== Definition: Schreibender Zugriff auf einen Bus (Senden) == | |||

<p> | <p> | ||

<loop_area type="definition"> | <loop_index id="5fa978806e4cc">Schreibender Zugriff, Bus|senden, Bus|Bus, schreibender Zugriff|Bus, senden</loop_index> | ||

<loop_area type="definition"> | |||

<p> | <p> | ||

Ein '''schreibender Zugriff''' auf einen Bus liegt vor, wenn eine an diesem Bus angeschlossene Komponente eine Gruppe von Bits zur Übertragung auf den Bus gibt. Man spricht dann auch vom '''Senden''' von Informationen über den Bus. | Ein '''schreibender Zugriff''' auf einen Bus liegt vor, wenn eine an diesem Bus angeschlossene Komponente eine Gruppe von Bits zur Übertragung auf den Bus gibt. Man spricht dann auch vom '''Senden''' von Informationen über den Bus. | ||

</p> | </p> | ||

| Zeile 103: | Zeile 126: | ||

<p> | <p> | ||

Nur eine einzige am Bus angeschlossene Komponente darf zur Zeit schreibend auf den Bus zugreifen. | Nur eine einzige am Bus angeschlossene Komponente darf zur gleichen Zeit schreibend auf den Bus zugreifen. | ||

</p> | </p> | ||

<br /> | |||

== Definition: Lesender Zugriff auf einen Bus (Empfangen) == | |||

<p> | <p> | ||

<loop_area type="definition"> | <loop_index id="5fa978806e4d6">Lesender Zugriff, Bus|empfangen, Bus|Bus, lesender Zugriff|Bus, empfangen</loop_index> | ||

<loop_area type="definition"> | |||

<p> | <p> | ||

Ein '''lesender Zugriff''' auf einen Bus liegt vor, wenn eine an diesem Bus angeschlossene Komponente eine Gruppe von Bits vom Bus entgegennimmt. Man spricht dann auch vom '''Empfangen''' von Informationen über den Bus. | Ein '''lesender Zugriff''' auf einen Bus liegt vor, wenn eine an diesem Bus angeschlossene Komponente eine Gruppe von Bits vom Bus entgegennimmt. Man spricht dann auch vom '''Empfangen''' von Informationen über den Bus. | ||

</p> | </p> | ||

| Zeile 119: | Zeile 145: | ||

</p> | </p> | ||

<br /> | |||

== Definition: Kollision auf einem Bus == | |||

<p> | <p> | ||

<loop_area type="definition"> | <loop_index id="5fa978806e4df">Kollision, Bus</loop_index> | ||

<loop_area type="definition"> | |||

<p> | <p> | ||

Eine '''Kollision''' auf einem Bus liegt vor, falls zur gleichen Zeit mehrere Komponenten schreibend auf den Bus zugreifen. | Eine '''Kollision''' auf einem Bus liegt vor, falls zur gleichen Zeit mehrere Komponenten schreibend auf den Bus zugreifen. | ||

| Zeile 131: | Zeile 161: | ||

</p> | </p> | ||

<br /> | |||

== Definition: Adressbus == | |||

<p> | <p> | ||

<loop_area type="definition"> | <loop_index id="5fa978806e4e8">Adressbus</loop_index><loop_index id="5fa978c40f376">Bus, Adressbus</loop_index> | ||

<loop_area type="definition"> | |||

<p> | <p> | ||

Ein '''Adressbus''' ist ein Bus, bei dem die parallel übertragene Gruppe von Bits als Adresse zu interpretieren ist. | Ein '''Adressbus''' ist ein Bus, bei dem die parallel übertragene Gruppe von Bits als Adresse zu interpretieren ist. | ||

</p> | </p> | ||

| Zeile 140: | Zeile 173: | ||

</p> | </p> | ||

<br /> | |||

== Definition: Datenbus == | |||

<p> | <p> | ||

<loop_area type="definition"> | <loop_index id="5fa978806e4f1">Datenbus</loop_index><loop_index id="5fa978813458f">Bus, Datenbus</loop_index> | ||

<loop_area type="definition"> | |||

<p> | <p> | ||

Ein '''Datenbus''' ist ein Bus, bei dem die parallel übertragene Gruppe von Bits als Daten zu interpretieren ist. | Ein '''Datenbus''' ist ein Bus, bei dem die parallel übertragene Gruppe von Bits als Daten zu interpretieren ist. | ||

</p> | </p> | ||

| Zeile 149: | Zeile 184: | ||

</p> | </p> | ||

<br /> | |||

== Detailliertere Sicht auf die Arbeitsweise des Steuerwerks == | |||

<p> | <p> | ||

Im folgenden Video wird die Arbeitsweise des Steuerwerks etwas detaillierter aufgeschlüsselt und erläutert. | Im folgenden Video wird die Arbeitsweise des Steuerwerks etwas detaillierter aufgeschlüsselt und erläutert. | ||

| Zeile 154: | Zeile 191: | ||

<p> | <p> | ||

<loop_media type="video" title="Detailliertere Arbeitsweise des Steuerwerks (06:01)" description="http://youtu.be/eEZIlmMHl7c" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|eEZIlmMHl7c}}</loop_media> | <loop_area icon="Video.png" icontext="Video"> | ||

<loop_media type="video" title="Detailliertere Arbeitsweise des Steuerwerks (06:01)" description="http://youtu.be/eEZIlmMHl7c" copyright="CC-BY" index=true show_copyright=true id="5fa978806e4fb">{{#ev:youtube|eEZIlmMHl7c|700}}</loop_media> | |||

</loop_area> | |||

</p> | </p> | ||

<br /> | |||

<p> | <p> | ||

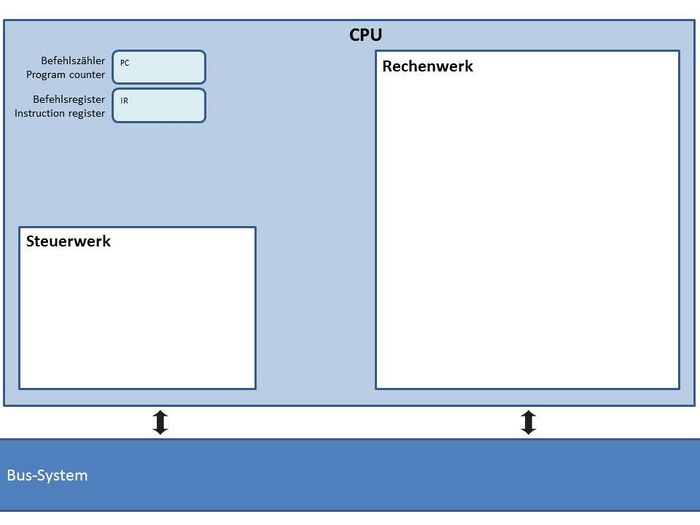

Die im Video erarbeitete detailliertere Sicht auf die Arbeitsweise des Steuerwerks sieht damit so aus: | Die im Video erarbeitete detailliertere Sicht auf die Arbeitsweise des Steuerwerks sieht damit so aus: | ||

| Zeile 162: | Zeile 202: | ||

<p> | <p> | ||

<loop_figure title="Eine detailliertere Sicht auf die Arbeitsweise des Steuerwerks" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Steuerwerk02.jpg|700px]]</loop_figure> | <loop_figure title="Eine detailliertere Sicht auf die Arbeitsweise des Steuerwerks" description="" copyright="CC-BY" index=true show_copyright=true id="5fa978806e503">[[Datei:Steuerwerk02.jpg|700px]]</loop_figure> | ||

</p> | </p> | ||

<br /> | |||

<p> | <p> | ||

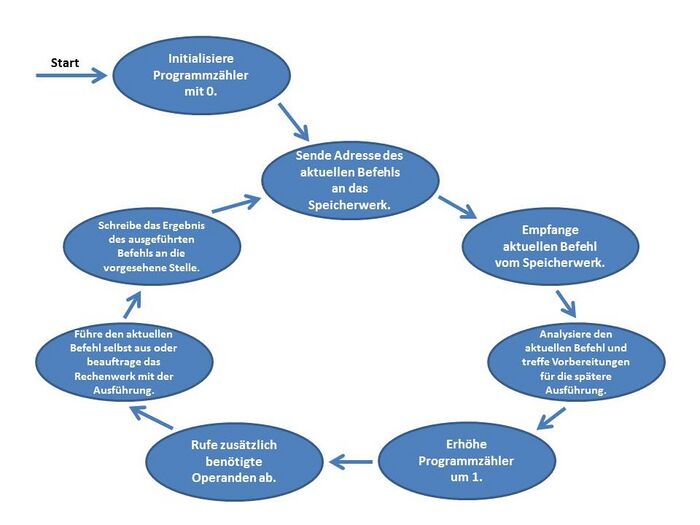

Und der aktuelle Stand bei der Erläuterung von CPU und insbesondere dem Steuerwerk ist: | Und der aktuelle Stand bei der Erläuterung von CPU und insbesondere dem Steuerwerk ist: | ||

| Zeile 170: | Zeile 211: | ||

<p> | <p> | ||

<loop_figure title="Steuerwerk mit Adress- und Datenbus" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Cpu3.jpg|700px]]</loop_figure> | <loop_figure title="Steuerwerk mit Adress- und Datenbus" description="" copyright="CC-BY" index=true show_copyright=true id="5fa978806e50c">[[Datei:Cpu3.jpg|700px]]</loop_figure> | ||

</p> | </p> | ||

Aktuelle Version vom 9. November 2020, 18:42 Uhr

Eines der Bestandteile der CPU ist das Steuerwerk:

Definition: Steuerwerk

Das Steuerwerk (oder Leitwerk) ist ein Bestandteil der CPU und für die sequentielle Abarbeitung des im Speicherwerk befindlichen Programms zuständig.

Damit ist sofort ersichtlich, dass eine Verbindung zwischen Steuerwerk und Speicherwerk existieren muss, damit das abzuarbeitende Programm, bzw. dessen einzelnen Anweisungen, vom Speicherwerk in das Steuerwerk übertragen werden können.

Definition: Arbeitsweise des Steuerwerks

Das Steuerwerk sendet die Adresse des aktuellen Befehls an das Speicherwerk und erhält von diesem als Antwort genau jenen Befehl, der an der übermittelten Adresse innerhalb des Speicherwerks steht. Sobald das Steuerwerk den Befehl erhalten hat, wird dieser ausgeführt.

Einfache Sicht auf die Arbeitsweise des Steuerwerks

Es ergibt sich damit für die Arbeitsweise des Steuerwerks ein Kreislauf, der immer wieder durchlaufen wird:

Diese Darstellung ist leicht verständlich, stellt aber auch nur eine erste vereinfachte Sicht auf die Arbeitsweise dar.

Bestandteile der CPU

Aus der einfachen Sicht der Arbeitsweise des Steuerwerks lassen sich einige Bestandteile der CPU ableiten:

- Damit die Adresse des aktuellen Befehls vom Steuerwerk verwaltet werden kann, muss es einen Speicherbereich dafür geben. Verwendet wird dazu ein Register, der sogenannte Befehlszähler, engl. Program Counter, kurz: PC.

- Damit der vom Speicherwerk empfangene Befehl verwaltet werden kann, muss es einen Speicherbereich dafür geben. Verwendet wird dazu ein Register, das sogenannte Befehlsregister, engl. Instruction Register, kurz: IR.

- Die Adresse des aktuellen Befehls kann über das vorhandene Bus-System an das Speicherwerk gesendet werden. Eine Verbindung der Register PC sowie IR mit dem Bus-System muss daher gegeben sein.

Erweitertes Bild der CPU

Man erhält ein leicht erweitertes Bild der CPU:

Zusammenspiel PC, IR und Bus

Das folgende Video geht näher auf das Zusammenspiel von Befehlszähler (PC) und Befehlsregister (IR) mit dem Bus-System ein. Die Fachbegriffe Adressbus und Datenbus werden eingeführt und erläutert.

Zu den Erläuterungen im Video folgen hier noch einige Definitionen.

Definition: (Paralleler) Bus

Ein Bus (Binary Unit System) dient zur parallelen Übertragung einer Gruppe von Bits.

Hinweis: Es wird hier ausdrücklich ein "paralleler Bus" definiert. Gleichzeitig sei darauf hingewiesen, dass auch "serielle Busse" existieren, die zum jetzigen Zeitpunkt in diesem Modul aber (noch) keine Rolle spielen.

Es können mehrere Komponenten an einem Bus angeschlossen sein, so dass sich Quelle und Ziel der übertragenen Bits benennen lassen.

Definition: Busbreite

Die Anzahl der parallel übertragbaren Bits auf einem Bus nennt man die Breite des Busses oder Busbreite.

Übliche Busbreiten in Vergangenheit und Gegenwart waren bzw. sind 4, 8, 16, 32 oder 64 Bit.

Definition: Schreibender Zugriff auf einen Bus (Senden)

Ein schreibender Zugriff auf einen Bus liegt vor, wenn eine an diesem Bus angeschlossene Komponente eine Gruppe von Bits zur Übertragung auf den Bus gibt. Man spricht dann auch vom Senden von Informationen über den Bus.

Nur eine einzige am Bus angeschlossene Komponente darf zur gleichen Zeit schreibend auf den Bus zugreifen.

Definition: Lesender Zugriff auf einen Bus (Empfangen)

Ein lesender Zugriff auf einen Bus liegt vor, wenn eine an diesem Bus angeschlossene Komponente eine Gruppe von Bits vom Bus entgegennimmt. Man spricht dann auch vom Empfangen von Informationen über den Bus.

Es können beliebig viele Komponenten zur gleichen Zeit Informationen über den Bus empfangen.

Definition: Kollision auf einem Bus

Eine Kollision auf einem Bus liegt vor, falls zur gleichen Zeit mehrere Komponenten schreibend auf den Bus zugreifen.

Beim Betreiben eines Busses ist also sicher zu stellen, dass immer nur eine Komponente zur Zeit schreibend auf den Bus zugreift. Falls einmal mehr als nur eine Komponente zur gleichen Zeit auf den Bus schreibt, so werden aufgrund der physikalischen Gesetze die übertragenen Bits unbrauchbar, d.h. sie können von den lesenden Komponenten am Bus nicht mehr verlässlich empfangen werden. Die übertragenen Informationen gehen verloren. (Siehe hierzu auch das Video im Abschnitt Von-Neumann-Flaschenhals).

Definition: Adressbus

Ein Adressbus ist ein Bus, bei dem die parallel übertragene Gruppe von Bits als Adresse zu interpretieren ist.

Definition: Datenbus

Ein Datenbus ist ein Bus, bei dem die parallel übertragene Gruppe von Bits als Daten zu interpretieren ist.

Detailliertere Sicht auf die Arbeitsweise des Steuerwerks

Im folgenden Video wird die Arbeitsweise des Steuerwerks etwas detaillierter aufgeschlüsselt und erläutert.

Die im Video erarbeitete detailliertere Sicht auf die Arbeitsweise des Steuerwerks sieht damit so aus:

Und der aktuelle Stand bei der Erläuterung von CPU und insbesondere dem Steuerwerk ist: