2.1.6 Gatter

| [gesichtete Version] | [gesichtete Version] |

Keine Bearbeitungszusammenfassung |

Kwastg (Diskussion | Beiträge) Keine Bearbeitungszusammenfassung |

||

| (16 dazwischenliegende Versionen von 3 Benutzern werden nicht angezeigt) | |||

| Zeile 1: | Zeile 1: | ||

<p> | <p> | ||

Im Kapitel [[Aufbau und Arbeitsweise eines Registers]] wird der Aufbau und die Arbeitsweise einer einzelnen Speicherzelle eines Registers der CPU erklärt (siehe Video: [http://youtu.be/W1fCLMbYrnw Arbeitsweise einer Speicherzelle]). Dabei kommen u.a. UND-Gatter zum Einsatz. | Im Kapitel [[Aufbau und Arbeitsweise eines Registers]] wird der Aufbau und die Arbeitsweise einer einzelnen Speicherzelle eines Registers der CPU erklärt (siehe Video: [http://youtu.be/W1fCLMbYrnw Arbeitsweise einer Speicherzelle]). Dabei kommen u.a. UND-Gatter zum Einsatz. | ||

| Zeile 4: | Zeile 5: | ||

<br /> | <br /> | ||

== Gatter-Typen == | |||

<p> | <p> | ||

Die folgende Abbildung zeigt weitere definierte Gatter-Typen: | Die folgende Abbildung zeigt weitere definierte Gatter-Typen: | ||

</p><loop_index>NICHT-Gatter|Gatter, NICHT|NOT-Gate|Gate, NOT</loop_index><loop_index>UND-Gatter|Gatter, UND|AND-Gate|Gate, AND</loop_index><loop_index>NICHT-UND-Gatter|Gatter, NICHT-UND|NAND-Gate|Gate, NAND</loop_index><loop_index>ODER-Gatter|Gatter, ODER|OR-Gate|Gate, OR</loop_index> | </p><loop_index id="5fa9785ca4710">NICHT-Gatter|Gatter, NICHT|NOT-Gate|Gate, NOT</loop_index><loop_index id="5fa9785ca4718">UND-Gatter|Gatter, UND|AND-Gate|Gate, AND</loop_index><loop_index id="5fa9785ca471d">NICHT-UND-Gatter|Gatter, NICHT-UND|NAND-Gate|Gate, NAND</loop_index><loop_index id="5fa9785ca4722">ODER-Gatter|Gatter, ODER|OR-Gate|Gate, OR</loop_index> | ||

<loop_index>NICHT-ODER-Gatter | <loop_index id="5fa9785ca4726">NICHT-ODER-Gatter</loop_index><loop_index id="5fa978ae58fbf">Gatter, NICHT-ODER</loop_index><loop_index id="5fa978ae58fc6">NOR-Gate</loop_index><loop_index id="5fa978ae58fcb">Gate, NOR</loop_index><loop_index id="5fa9785ca472b">EXKLUSIV-ODER-Gatter</loop_index><loop_index id="5fa9785d19682">Gatter, EXCLUSIV-ODER</loop_index><loop_index id="5fa9785d19688">XOR-Gate</loop_index><loop_index id="5fa9785d1968e">Gate, XOR</loop_index> | ||

<p> | <p> | ||

<loop_figure title="Unterschiedliche Gatter" description="Symbole gemäß IEEE Standard 91a-1991" copyright="CC-BY" index=true show_copyright=true>[[Datei:Gatter.jpg|650px]]</loop_figure> | <loop_figure title="Unterschiedliche Gatter" description="Symbole gemäß IEEE Standard 91a-1991" copyright="CC-BY" index=true show_copyright=true id="5fa9785ca472f">[[Datei:Gatter.jpg|650px]]</loop_figure> | ||

</p> | </p> | ||

<br /> | <br /> | ||

== Wahrheitstafeln == | |||

<p> | <p> | ||

Die für die Gatter geltenden Ausgangswerte in Abhängigkeit der Eingangswerte zeigen die folgenden <loop_index>Wahrheitstafel</loop_index>Wahrheitstafeln: | Die für die Gatter geltenden Ausgangswerte in Abhängigkeit der Eingangswerte zeigen die folgenden <loop_index id="5fa9785ca4734">Wahrheitstafel</loop_index>Wahrheitstafeln: | ||

</p> | </p> | ||

<p> | <p> | ||

<loop_figure title="Wahrheitstafel für Gatter" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Wahrheitstafel_gatter.jpg|650px]]</loop_figure> | <loop_figure title="Wahrheitstafel für Gatter" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9785ca4738">[[Datei:Wahrheitstafel_gatter.jpg|650px]]</loop_figure> | ||

</p> | </p> | ||

<br /> | <br /> | ||

== Zusammenhang == | |||

<p> | <p> | ||

Das folgende Video verdeutlich den Zusammenhang des jeweiligen Gatters mit seiner Wahrheitstafel. | Das folgende Video verdeutlich den Zusammenhang des jeweiligen Gatters mit seiner Wahrheitstafel. | ||

| Zeile 31: | Zeile 32: | ||

<p> | <p> | ||

<loop_area icon="Video.png" icontext="Video"> | <loop_area icon="Video.png" icontext="Video"> | ||

<loop_media type="video" title="Gatter und ihre Wahrheitstafeln (02:56)" description="http://youtu.be/-MXBdtikhzw" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|-MXBdtikhzw|700}}</loop_media> | <loop_media type="video" title="Gatter und ihre Wahrheitstafeln (02:56)" description="http://youtu.be/-MXBdtikhzw" copyright="CC-BY" index=true show_copyright=true id="5fa9785ca473d">{{#ev:youtube|-MXBdtikhzw|700}}</loop_media> | ||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

| Zeile 55: | Zeile 56: | ||

<br /> | <br /> | ||

== | == Transistoren, Gatter und Addierer auf der CPU == | ||

<p> | <p> | ||

<loop_area type=" | <loop_area type="websource"> | ||

<p> | <p> | ||

Eine sehr schöne (englischsprachige) Erläuterung des Zusammenhangs zwischen Transistoren, Gatter und Addierer auf einer CPU bietet das folgende Video (14:26) auf YouTube: | Eine sehr schöne (englischsprachige) Erläuterung des Zusammenhangs zwischen Transistoren, Gatter und Addierer auf einer CPU bietet das folgende Video (14:26) auf YouTube: | ||

</p> | </p> | ||

<p> | <p> | ||

<loop_index>See How Computers Add Numbers In One Lesson, Video</loop_index> | <loop_index id="5fa9785ca4742">See How Computers Add Numbers In One Lesson, Video</loop_index> | ||

[https://www.youtube.com/watch?v=VBDoT8o4q00 See How Computers Add Numbers In One Lesson]<br />[http://www.youtube.com/watch?v=VBDoT8o4q00 http://www.youtube.com/watch?v=VBDoT8o4q00] | [https://www.youtube.com/watch?v=VBDoT8o4q00 See How Computers Add Numbers In One Lesson]<br />[http://www.youtube.com/watch?v=VBDoT8o4q00 http://www.youtube.com/watch?v=VBDoT8o4q00] | ||

</p> | </p> | ||

| Zeile 69: | Zeile 69: | ||

Schau es dir an! | Schau es dir an! | ||

</p> | </p> | ||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

Aktuelle Version vom 9. November 2020, 19:46 Uhr

Im Kapitel Aufbau und Arbeitsweise eines Registers wird der Aufbau und die Arbeitsweise einer einzelnen Speicherzelle eines Registers der CPU erklärt (siehe Video: Arbeitsweise einer Speicherzelle). Dabei kommen u.a. UND-Gatter zum Einsatz.

Gatter-Typen

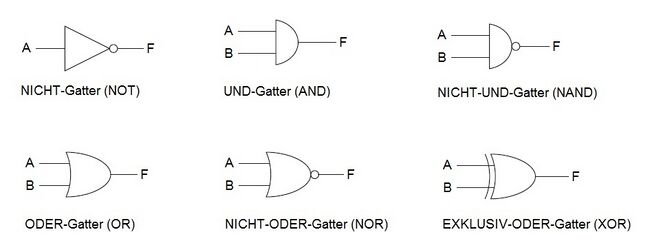

Die folgende Abbildung zeigt weitere definierte Gatter-Typen:

Wahrheitstafeln

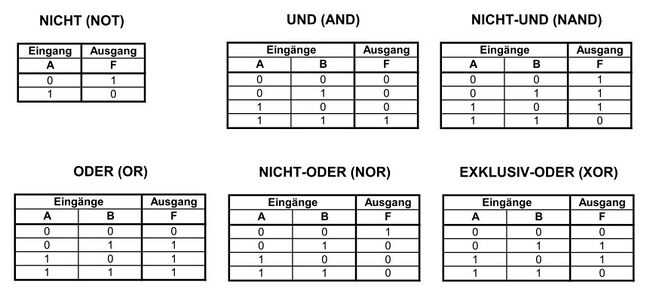

Die für die Gatter geltenden Ausgangswerte in Abhängigkeit der Eingangswerte zeigen die folgenden Wahrheitstafeln:

Zusammenhang

Das folgende Video verdeutlich den Zusammenhang des jeweiligen Gatters mit seiner Wahrheitstafel.

Zusätzliche Bescheibungen, auch zum internen Aufbau eines einzelnen Gatters, liefert die weiterführende Literatur:

Weiterführende Literatur

Die hier verlinkte Online-Ausgabe eines Lehrtextes der Otto-Friedrich-Universität Bamberg liefert in Kapitel 4: Schaltwerke detailliertere Informationen zum Aufbau eines Registers und seiner Speicherzellen. Die Lektüre dieser Quelle sei unter Beachtung der geltenden Lizenz ausdrücklich empfohlen.

Autoren: Martin Eisenhardt, Andreas Henrich, Stefanie Sieber

Rechner- und Betriebssysteme, Kommunikationssysteme, Verteilte Systeme

http://www.uni-bamberg.de/fileadmin/uni/fakultaeten/wiai_lehrstuehle/medieninformatik/Dateien/Publikationen/2007/eisenhardt-rbkvs-1.0.pdf

Dieses Werk steht unter der Creative Commons BY-NC-ND-Lizenz

http://creativecommons.org/licenses/by-nc-nd/2.0/de/

Transistoren, Gatter und Addierer auf der CPU

Eine sehr schöne (englischsprachige) Erläuterung des Zusammenhangs zwischen Transistoren, Gatter und Addierer auf einer CPU bietet das folgende Video (14:26) auf YouTube:

See How Computers Add Numbers In One Lesson

http://www.youtube.com/watch?v=VBDoT8o4q00

Schau es dir an!