2.1.5.1 Aufbau und Arbeitsweise eines Registers

| [gesichtete Version] | [gesichtete Version] |

Keine Bearbeitungszusammenfassung |

Keine Bearbeitungszusammenfassung |

||

| Zeile 7: | Zeile 7: | ||

Die Speicherzelle besteht aus einem sogenannten RS-Flip-Flop, sowie drei UND-Gattern. | Die Speicherzelle besteht aus einem sogenannten RS-Flip-Flop, sowie drei UND-Gattern. | ||

<loop_area type="notice">'''Hinweis'''<br> | <loop_area type="notice">'''Hinweis'''<br> | ||

Die hier verlinkte Online-Ausgabe eines Lehrtextes der Otto-Friedrich-Universität Bamberg liefert in Kapitel 5.2 und 5.3 detailliertere Informationen zum Aufbau eines Registers und seiner Speicherzellen. In weiteren Kapiteln finden sich darüber hinaus zusätzlich relevante Erläuterungen. Die Lektüre dieser Quelle sei unter Beachtung der geltenden Lizenz ausdrücklich empfohlen. | Die hier verlinkte Online-Ausgabe eines Lehrtextes der Otto-Friedrich-Universität Bamberg liefert in Kapitel 5.2 und 5.3 detailliertere Informationen zum Aufbau eines Registers und seiner Speicherzellen. In weiteren Kapiteln finden sich darüber hinaus zusätzlich relevante Erläuterungen zum Themengebiet. Die Lektüre dieser Quelle sei unter Beachtung der geltenden Lizenz ausdrücklich empfohlen.<br /><br />Autoren: Martin Eisenhardt, Andreas Henrich, Stefanie Sieber<br />[http://www.uni-bamberg.de/fileadmin/uni/fakultaeten/wiai_lehrstuehle/medieninformatik/Dateien/Publikationen/2007/eisenhardt-rbkvs-1.0.pdf '''Rechner- und Betriebssysteme, Kommunikationssysteme, Verteilte Systeme''']<br />http://www.uni-bamberg.de/fileadmin/uni/fakultaeten/wiai_lehrstuehle/medieninformatik/Dateien/Publikationen/2007/eisenhardt-rbkvs-1.0.pdf<br /><br />Dieses Werk steht unter der Creative Commons BY-NC-ND-Lizenz<br />http://creativecommons.org/licenses/by-nc-nd/2.0/de/ | ||

<br />Autoren: Martin Eisenhardt, Andreas Henrich, Stefanie Sieber<br />[http://www.uni-bamberg.de/fileadmin/uni/fakultaeten/wiai_lehrstuehle/medieninformatik/Dateien/Publikationen/2007/eisenhardt-rbkvs-1.0.pdf '''Rechner- und Betriebssysteme, Kommunikationssysteme, Verteilte Systeme''']<br />http://www.uni-bamberg.de/fileadmin/uni/fakultaeten/wiai_lehrstuehle/medieninformatik/Dateien/Publikationen/2007/eisenhardt-rbkvs-1.0.pdf<br />Dieses Werk steht unter der Creative Commons BY-NC-ND-Lizenz<br />http://creativecommons.org/licenses/by-nc-nd/2.0/de/ | |||

</loop_area> | </loop_area> | ||

<br /> | <br /> | ||

Version vom 30. August 2013, 17:08 Uhr

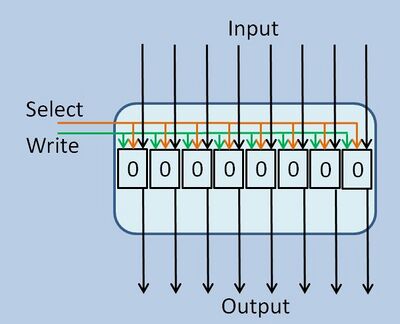

Register sind kleine Speichereinheiten, die sich direkt auf der CPU befinden. Den internen Aufbau und die Arbeitsweise eines 8-Bit-Registers erläutert das folgende Video.

Ein Register besteht aus einzelnen Speicherzellen. Jede Speicherzelle kann dabei den Wert von genau einem Bit aufnehmen.

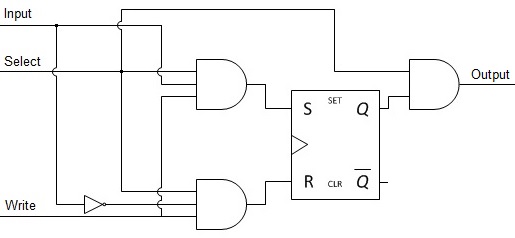

Der interne Aufbau einer einzelnen Speicherzelle sieht wie folgt aus:

Die Speicherzelle besteht aus einem sogenannten RS-Flip-Flop, sowie drei UND-Gattern.

Hinweis

Die hier verlinkte Online-Ausgabe eines Lehrtextes der Otto-Friedrich-Universität Bamberg liefert in Kapitel 5.2 und 5.3 detailliertere Informationen zum Aufbau eines Registers und seiner Speicherzellen. In weiteren Kapiteln finden sich darüber hinaus zusätzlich relevante Erläuterungen zum Themengebiet. Die Lektüre dieser Quelle sei unter Beachtung der geltenden Lizenz ausdrücklich empfohlen.

Autoren: Martin Eisenhardt, Andreas Henrich, Stefanie Sieber

Rechner- und Betriebssysteme, Kommunikationssysteme, Verteilte Systeme

http://www.uni-bamberg.de/fileadmin/uni/fakultaeten/wiai_lehrstuehle/medieninformatik/Dateien/Publikationen/2007/eisenhardt-rbkvs-1.0.pdf

Dieses Werk steht unter der Creative Commons BY-NC-ND-Lizenz

http://creativecommons.org/licenses/by-nc-nd/2.0/de/

Diese Seite steht unter der Creative Commons Namensnennung 3.0 Unported Lizenz http://i.creativecommons.org/l/by/3.0/80x15.png