2.1.5.1 Aufbau und Arbeitsweise eines Registers

| [gesichtete Version] | [gesichtete Version] |

Keine Bearbeitungszusammenfassung |

|||

| (55 dazwischenliegende Versionen von 9 Benutzern werden nicht angezeigt) | |||

| Zeile 1: | Zeile 1: | ||

Register sind gemäß ihrer Definition kleine Speichereinheiten, die sich direkt auf der CPU befinden. Den internen Aufbau und die Arbeitsweise eines 8-Bit-Registers erläutert das folgende Video. | |||

<p><loop_media type="video" title="Aufbau und Arbeitsweise eines Registers (04:40)" description="http://youtu.be/CUxnaaZozVM" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|CUxnaaZozVM}}</loop_media></p> | <p> | ||

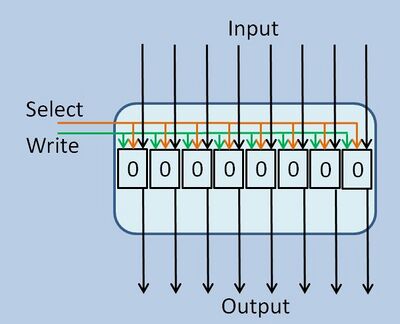

Ein Register besteht aus einzelnen Speicherzellen. Jede Speicherzelle kann dabei den Wert von genau einem Bit aufnehmen. Ein Register der Breite acht besitzt demnach acht Speicherzellen. Jede Speicherzelle verfügt über eine separate Input- sowie Output-Leitung. Die Select- und Write-Leitung steht einmal für alle Speicherzellen zur Verfügung. | <loop_index id="5fa9784008db5">Register|Aufbau, Register|Arbeitsweise, Register|Register, Aufbau|Register, Arbeitsweise</loop_index>Register sind gemäß ihrer Definition kleine <loop_index id="5fa9784008dc2">Speichereinheit, Register</loop_index>Speichereinheiten, die sich direkt auf der CPU befinden. Den internen Aufbau und die Arbeitsweise eines <loop_index id="5fa9784008dcc">8-Bit-Register|Register, 8-Bit</loop_index>8-Bit-Registers erläutert das folgende Video. | ||

<p><loop_figure title="Register mit 8 Speicherzellen" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Register01.jpg|400px]]</loop_figure></p> | </p> | ||

<p> | |||

<loop_area icon="Video.png" icontext="Video"> | |||

<loop_media type="video" title="Aufbau und Arbeitsweise eines Registers (04:40)" description="http://youtu.be/CUxnaaZozVM" copyright="CC-BY" index=true show_copyright=true id="5fa9784008dd6">{{#ev:youtube|CUxnaaZozVM|700}}</loop_media> | |||

</loop_area> | |||

</p> | |||

<p> | |||

Ein Register besteht aus einzelnen <loop_index id="5fa9784008de0">Speicherzelle</loop_index>Speicherzellen. Jede Speicherzelle kann dabei den Wert von genau einem Bit aufnehmen. Ein Register der Breite acht besitzt demnach acht Speicherzellen. | |||

</p> | |||

<br > | |||

== Aufbau einer Speicherzelle == | |||

<p> | |||

<loop_index id="5fa9784008de9">Aufbau, Speicherzelle|Speicherzelle, Aufbau</loop_index> | |||

Jede Speicherzelle verfügt über eine separate <loop_index id="5fa9784008df3">Input-Leitung, Speicherzelle|Speicherzelle, Input-Leitung</loop_index>Input- sowie <loop_index id="5fa9784008dfc">Output-Leitung, Speicherzelle|Speicherzelle, Output-Leitung</loop_index>Output-Leitung. Die <loop_index id="5fa9784008e05">Select-Leitung, Speicherzelle|Speicherzelle, Select-Leitung</loop_index>Select- und <loop_index id="5fa9784008e0f">Write-Leitung, Speicherzelle|Speicherzelle, Write-Leitung</loop_index>Write-Leitung steht einmal für alle Speicherzellen zur Verfügung. | |||

</p> | |||

<p> | |||

<loop_figure title="Register mit 8 Speicherzellen" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9784008e18">[[Datei:Register01.jpg|400px]]</loop_figure> | |||

</p> | |||

<br /> | |||

<p> | |||

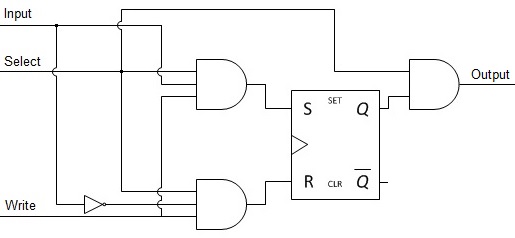

Der interne Aufbau einer einzelnen Speicherzelle sieht wie folgt aus: | Der interne Aufbau einer einzelnen Speicherzelle sieht wie folgt aus: | ||

<p><loop_figure title="Aufbau einer einzelnen Speicherzelle" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Speicherzelle02.jpg]]</loop_figure></p> | </p> | ||

Die Speicherzelle besteht aus einem sogenannten RS-Flip-Flop, drei UND-Gattern, einem NICHT-Gatter sowie der notwendigen Verdrahtung. | |||

<p> | |||

<loop_figure title="Aufbau einer einzelnen Speicherzelle" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9784008e22">[[Datei:Speicherzelle02.jpg]]</loop_figure> | |||

</p> | |||

<p> | |||

Die Speicherzelle besteht aus einem sogenannten <loop_index id="5fa9784008e2b">RS-Flip-Flop|Flip-Flop, RS-Flip-Flop</loop_index>RS-Flip-Flop, drei <loop_index id="5fa9784008e34">UND-Gatter|Gatter, UND|AND-Gate|Gate, AND</loop_index>UND-Gattern, einem <loop_index id="5fa9784008e3d">NICHT-Gatter|Gatter, NICHT|NOT-Gate|Gate, NOT</loop_index>NICHT-Gatter sowie der notwendigen <loop_index id="5fa9784008e46">Verdrahtung, Gatter|Gatter, Verdrahtung</loop_index>Verdrahtung. | |||

</p> | |||

<br /> | |||

== Arbeitsweise einer Speicherzelle == | |||

<p> | |||

<loop_index id="5fa9784008e4e">Arbeitsweise, Speicherzelle|Speicherzelle, Arbeitsweise</loop_index> | |||

Das folgende Video erklärt die Arbeitsweise der Speicherzelle: | Das folgende Video erklärt die Arbeitsweise der Speicherzelle: | ||

<p><loop_media type="video" title="Arbeitsweise einer Speicherzelle (04:49)" description="http://youtu.be/W1fCLMbYrnw" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|W1fCLMbYrnw}}</loop_media></p> | </p> | ||

Hier folgen die im Video gezeigten Wahrheitstafeln der UND-Gatter: | |||

<p><loop_figure title="Wahrheitstafeln von UND-Gattern mit zwei bzw. drei Eingängen" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei: | <p> | ||

<loop_area icon="Video.png" icontext="Video"> | |||

<loop_media type="video" title="Arbeitsweise einer Speicherzelle (04:49)" description="http://youtu.be/W1fCLMbYrnw" copyright="CC-BY" index=true show_copyright=true id="5fa9784008e58">{{#ev:youtube|W1fCLMbYrnw|700}}</loop_media> | |||

</loop_area> | |||

</p> | |||

<br /> | |||

== Wahrheitstafeln == | |||

<p> | |||

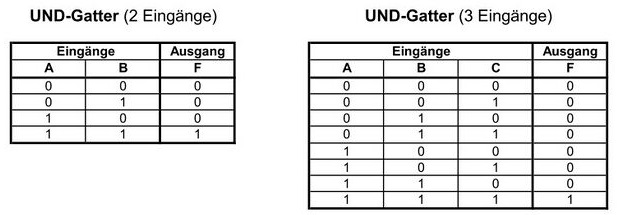

Hier folgen die im Video gezeigten <loop_index id="5fa9784008e60">Wahrheitstafel</loop_index>Wahrheitstafeln der UND-Gatter: | |||

</p> | |||

<p> | |||

<loop_figure title="Wahrheitstafeln von UND-Gattern mit zwei bzw. drei Eingängen" description="" copyright="CC-BY" index=true show_copyright=true id="5ff1a873177ab">[[Datei:Wahrheitstafel UND-Gatter.jpg|617px]]</loop_figure> | |||

</p> | |||

<br /> | |||

<br /> | |||

<p> | |||

Neben dem hier gezeigten UND-Gatter gibt es noch eine Reihe weiterer Gatter. Diese werden treffenderweise im Kapitel [[Gatter]] beschrieben. | Neben dem hier gezeigten UND-Gatter gibt es noch eine Reihe weiterer Gatter. Diese werden treffenderweise im Kapitel [[Gatter]] beschrieben. | ||

</p> | |||

<br /> | |||

<br /> | |||

<p> | |||

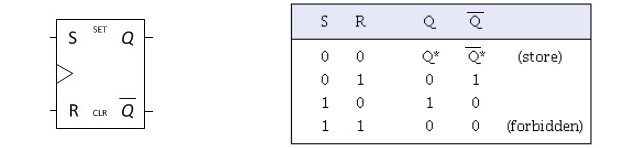

Auch das Verhalten des RS-Flip-Flop lässt sich mit einer Wahrheitstafel beschreiben: | |||

</p> | |||

<p> | |||

<loop_figure title="RS-Flip-Flop und die zugehörige Wahrheitstafel" description="" copyright="CC-BY" index=true show_copyright=true id="5ff1a63f2c170">[[Datei:RS-FlipFlop mit WT.jpg|639px]]</loop_figure> | |||

</p> | |||

<br /> | |||

<loop_area type="task"> | == Aufgabe 1 == | ||

Im RS-Flip-Flop ist der Wert '''''Null''''' gespeichert. Die Eingangsleitungen besitzen folgende Werte: | <p id="Aufgabe 1: Flip-Flop I"> | ||

<loop_area type="task"> | |||

<loop_task title="Flip-Flop I" id="5fa9784008e73"> | |||

<p> | |||

Im RS-Flip-Flop ist der Wert '''''Null''''' gespeichert. Die <loop_index id="5fa9784008e7c">Eingangsleitung|Eingangsleitung, RS-FlipFlop|RS-Flip-Flop, Eingangsleitung|Flip-Flop, Eingangsleitung</loop_index>Eingangsleitungen besitzen folgende Werte: | |||

* Input = 1 | * Input = 1 | ||

* Select = 1 | * Select = 1 | ||

* Write = 0 | * Write = 0 | ||

Welcher Wert wird unter diesen Voraussetzungen für den Ausgang (Output) der Speicherzelle ermittelt? | </p> | ||

<p> | |||

Welcher Wert wird unter diesen Voraussetzungen für den <loop_index id="5fa9784008e85">Ausgangsleitung|Ausgangsleitung, RS-FlipFlop|RS-Flip-Flop, Ausgangsleitung|Flip-Flop, Ausgangsleitung</loop_index>Ausgang (Output) der Speicherzelle ermittelt? | |||

</p> | |||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | |||

<loop_area type="task"> | <br /> | ||

== Aufgabe 2 == | |||

<p id="Aufgabe 2: Flip-Flop II"> | |||

<loop_area type="task"> | |||

<loop_task title="Flip-Flop II" id="5fa9784008e8d"> | |||

<p> | |||

Im RS-Flip-Flop ist der Wert '''''Eins''''' gespeichert. Die Eingangsleitungen besitzen folgende Werte: | Im RS-Flip-Flop ist der Wert '''''Eins''''' gespeichert. Die Eingangsleitungen besitzen folgende Werte: | ||

* Input = 1 | * Input = 1 | ||

* Select = 1 | * Select = 1 | ||

* Write = 0 | * Write = 0 | ||

Welcher Wert wird unter diesen Voraussetzungen für den Ausgang (Output) der Speicherzelle ermittelt?< | </p> | ||

<p> | |||

Welcher Wert wird unter diesen Voraussetzungen für den Ausgang (Output) der Speicherzelle ermittelt? | |||

</p> | |||

<p> | |||

<sub>(Die Werte für Input, Select und Write sind identisch mit denen aus Aufgabe 1, jedoch unterscheidet sich der im Flip-Flop gespeicherte Wert!)</sub> | <sub>(Die Werte für Input, Select und Write sind identisch mit denen aus Aufgabe 1, jedoch unterscheidet sich der im Flip-Flop gespeicherte Wert!)</sub> | ||

</p> | |||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | |||

<loop_area type="task"> | <br /> | ||

== Aufgabe 3 == | |||

<p id="Aufgabe 3: Flip-Flop III"> | |||

<loop_area type="task"> | |||

<loop_task title="Flip-Flop III" id="5fa9784008e96"> | |||

<p> | |||

Welchen Wert gibt das RS-Flip-Flop am Ausgang Q aus, wenn beide Eingänge gleich Null sind (S=0, R=0)? | Welchen Wert gibt das RS-Flip-Flop am Ausgang Q aus, wenn beide Eingänge gleich Null sind (S=0, R=0)? | ||

</p> | |||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | |||

<loop_area type="task"> | <br /> | ||

== Aufgabe 4 == | |||

<p id="Aufgabe 4: Simulationsframework Hades"> | |||

<loop_area type="task"> | |||

<loop_task title="Simulationsframework Hades" id="5fa9784008e9f"> | |||

<p> | |||

Norman Hendrich von der Universität Hamburg hat mit [http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/index.html Hades]<loop_index id="5fa9784008ea8">Hades|Hades Framework|Hades Simulationsframework</loop_index> ein <loop_index id="5fa9784008eb1">Simulationsframework Hades|Framework Hades</loop_index>Simulationsframework bereitgestellt, welches u.a. den internen Aufbau und die <loop_index id="5fa9784008eba">Arbeitsweise, RS-Flip-Flop</loop_index><loop_index id="5fa978988e143">Flip-Flop, Arbeitsweise</loop_index><loop_index id="5fa978988e14f">RS-Flip-Flop, Arbeitsweise</loop_index>Arbeitsweise eines RS-Flip-Flops per Applet im Browser veranschaulicht. Probiere es aus unter: | |||

</p> | |||

<p> | |||

<small>http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/16-flipflops/10-srff/srff.html</small> | <small>http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/16-flipflops/10-srff/srff.html</small> | ||

</p> | |||

<p> | |||

Du erkennst hier: Auch ein RS-Flip-Flop ist nichts anderes als eine digitale Schaltung bestehend aus einfachen Gattern. | Du erkennst hier: Auch ein RS-Flip-Flop ist nichts anderes als eine digitale Schaltung bestehend aus einfachen Gattern. | ||

</p> | |||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | |||

<loop_area type="notice"><span style="color:#ff0000;"><p> | |||

<p><small>Diese Seite war zuletzt nicht mehr direkt erreichbar. Allerdings existiert noch eine statische Kopie beim Internet Archive (ohne Applets, aber mit Wahrheitstafeln): https://web.archive.org/web/20110830134111/http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/16-flipflops/10-srff/srff.html</small> | |||

</p></span></loop_area> | |||

<br /> | <br /> | ||

<loop_area type=" | |||

== Aufgabe 5 == | |||

<p id="Aufgabe 5: Forbidden"> | |||

<loop_area type="task"> | |||

<loop_task title="Forbidden (RS-Flip-Flop)" id="5fa9784008ec2"> | |||

<p> | |||

In den im Applet auf der [http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/16-flipflops/10-srff/srff.html Hades-Seite] aus der vorangegangenen Aufgabe angegebenen Wahrheitstafeln gibt es jeweils den Hinweis "forbidden". | |||

* Was ist mit "forbidden"<loop_index id="5fa9784008ecb">forbidden, RS-Flip-Flop</loop_index><loop_index id="5fa97840a3018">RS-Flip-Flop, forbidden</loop_index> gemeint? | |||

* Welche Voraussetzung muss an den Eingangsleitungen erfüllt sein, damit der mit "forbidden" gekennzeichnete Zustand eintritt? | |||

* Wie realistisch schätzt du das Eintreten dieser Voraussetzung ein? | |||

</p> | |||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | |||

<br /> | <br /> | ||

< | <p> | ||

< | <loop_area type="notice">'''Weiterführende Literatur''' | ||

</ | <p> | ||

Die hier verlinkte Online-Ausgabe eines Lehrtextes der Otto-Friedrich-Universität Bamberg liefert in '''Kapitel 5.2 und 5.3''' detailliertere Informationen zum Aufbau eines Registers und seiner Speicherzellen. In weiteren Kapiteln finden sich darüber hinaus ergänzende Erläuterungen zum Themengebiet. Die Lektüre dieser Quelle sei unter Beachtung der geltenden Lizenz ausdrücklich empfohlen. | |||

</p> | |||

<p> | |||

Autoren: Martin Eisenhardt, Andreas Henrich, Stefanie Sieber<br />[http://www.uni-bamberg.de/fileadmin/uni/fakultaeten/wiai_lehrstuehle/medieninformatik/Dateien/Publikationen/2007/eisenhardt-rbkvs-1.0.pdf '''Rechner- und Betriebssysteme, Kommunikationssysteme, Verteilte Systeme'''] | |||

</p> | |||

<p> | |||

Dieses Werk steht unter der Creative Commons BY-NC-ND-Lizenz<br />http://creativecommons.org/licenses/by-nc-nd/2.0/de/ | |||

</p> | |||

</loop_area> | |||

</p> | |||

Aktuelle Version vom 3. Januar 2021, 13:20 Uhr

Register sind gemäß ihrer Definition kleine Speichereinheiten, die sich direkt auf der CPU befinden. Den internen Aufbau und die Arbeitsweise eines 8-Bit-Registers erläutert das folgende Video.

Ein Register besteht aus einzelnen Speicherzellen. Jede Speicherzelle kann dabei den Wert von genau einem Bit aufnehmen. Ein Register der Breite acht besitzt demnach acht Speicherzellen.

Aufbau einer Speicherzelle

Jede Speicherzelle verfügt über eine separate Input- sowie Output-Leitung. Die Select- und Write-Leitung steht einmal für alle Speicherzellen zur Verfügung.

Der interne Aufbau einer einzelnen Speicherzelle sieht wie folgt aus:

Die Speicherzelle besteht aus einem sogenannten RS-Flip-Flop, drei UND-Gattern, einem NICHT-Gatter sowie der notwendigen Verdrahtung.

Arbeitsweise einer Speicherzelle

Das folgende Video erklärt die Arbeitsweise der Speicherzelle:

Wahrheitstafeln

Hier folgen die im Video gezeigten Wahrheitstafeln der UND-Gatter:

Neben dem hier gezeigten UND-Gatter gibt es noch eine Reihe weiterer Gatter. Diese werden treffenderweise im Kapitel Gatter beschrieben.

Auch das Verhalten des RS-Flip-Flop lässt sich mit einer Wahrheitstafel beschreiben:

Aufgabe 1

Im RS-Flip-Flop ist der Wert Null gespeichert. Die Eingangsleitungen besitzen folgende Werte:

- Input = 1

- Select = 1

- Write = 0

Welcher Wert wird unter diesen Voraussetzungen für den Ausgang (Output) der Speicherzelle ermittelt?

Aufgabe 2

Im RS-Flip-Flop ist der Wert Eins gespeichert. Die Eingangsleitungen besitzen folgende Werte:

- Input = 1

- Select = 1

- Write = 0

Welcher Wert wird unter diesen Voraussetzungen für den Ausgang (Output) der Speicherzelle ermittelt?

(Die Werte für Input, Select und Write sind identisch mit denen aus Aufgabe 1, jedoch unterscheidet sich der im Flip-Flop gespeicherte Wert!)

Aufgabe 3

Welchen Wert gibt das RS-Flip-Flop am Ausgang Q aus, wenn beide Eingänge gleich Null sind (S=0, R=0)?

Aufgabe 4

Norman Hendrich von der Universität Hamburg hat mit Hades ein Simulationsframework bereitgestellt, welches u.a. den internen Aufbau und die Arbeitsweise eines RS-Flip-Flops per Applet im Browser veranschaulicht. Probiere es aus unter:

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/16-flipflops/10-srff/srff.html

Du erkennst hier: Auch ein RS-Flip-Flop ist nichts anderes als eine digitale Schaltung bestehend aus einfachen Gattern.

Diese Seite war zuletzt nicht mehr direkt erreichbar. Allerdings existiert noch eine statische Kopie beim Internet Archive (ohne Applets, aber mit Wahrheitstafeln): https://web.archive.org/web/20110830134111/http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/16-flipflops/10-srff/srff.html

Aufgabe 5

In den im Applet auf der Hades-Seite aus der vorangegangenen Aufgabe angegebenen Wahrheitstafeln gibt es jeweils den Hinweis "forbidden".

- Was ist mit "forbidden" gemeint?

- Welche Voraussetzung muss an den Eingangsleitungen erfüllt sein, damit der mit "forbidden" gekennzeichnete Zustand eintritt?

- Wie realistisch schätzt du das Eintreten dieser Voraussetzung ein?

Weiterführende Literatur

Die hier verlinkte Online-Ausgabe eines Lehrtextes der Otto-Friedrich-Universität Bamberg liefert in Kapitel 5.2 und 5.3 detailliertere Informationen zum Aufbau eines Registers und seiner Speicherzellen. In weiteren Kapiteln finden sich darüber hinaus ergänzende Erläuterungen zum Themengebiet. Die Lektüre dieser Quelle sei unter Beachtung der geltenden Lizenz ausdrücklich empfohlen.

Autoren: Martin Eisenhardt, Andreas Henrich, Stefanie Sieber

Rechner- und Betriebssysteme, Kommunikationssysteme, Verteilte Systeme

Dieses Werk steht unter der Creative Commons BY-NC-ND-Lizenz

http://creativecommons.org/licenses/by-nc-nd/2.0/de/