2.3.4.4 Kommunikation mit E/A-Geräten

| [gesichtete Version] | [gesichtete Version] |

Keine Bearbeitungszusammenfassung |

Keine Bearbeitungszusammenfassung |

||

| Zeile 59: | Zeile 59: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Aufgabe 1"> | |||

<p> | <p> | ||

Auf das Datenregister eines Controllers kann die CPU sowohl lesend, als auch schreibend zugreifen. Wie verhält es sich aber beim Steuer- und beim Zustandsregister? Ist der Zugriff hier ''nur lesend'', ''nur schreibend'' oder ''lesend und schreibend'' möglich? | Auf das Datenregister eines Controllers kann die CPU sowohl lesend, als auch schreibend zugreifen. Wie verhält es sich aber beim Steuer- und beim Zustandsregister? Ist der Zugriff hier ''nur lesend'', ''nur schreibend'' oder ''lesend und schreibend'' möglich? | ||

</p> | </p> | ||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

| Zeile 121: | Zeile 123: | ||

<p> | <p> | ||

<loop_area icon="Video.png" icontext="Video"> | |||

<loop_media type="video" title="Ein- und Ausgabe mit Festplatte und Interrupts (04:00)" description="http://youtu.be/nOEW4I_QX2c" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|nOEW4I_QX2c|700}}</loop_media> | <loop_media type="video" title="Ein- und Ausgabe mit Festplatte und Interrupts (04:00)" description="http://youtu.be/nOEW4I_QX2c" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|nOEW4I_QX2c|700}}</loop_media> | ||

</loop_area> | |||

</p> | </p> | ||

| Zeile 178: | Zeile 182: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Aufgabe 2"> | |||

<p> | <p> | ||

Im [http://youtu.be/nOEW4I_QX2c Video] wird gezeigt, wie die CPU wartet, und wartet, und wartet. Das ist natürlich keine gute Idee im Hinblick auf die Geschwindigkeit des Gesamtsystems. | Im [http://youtu.be/nOEW4I_QX2c Video] wird gezeigt, wie die CPU wartet, und wartet, und wartet. Das ist natürlich keine gute Idee im Hinblick auf die Geschwindigkeit des Gesamtsystems. | ||

| Zeile 184: | Zeile 189: | ||

* Eigentlich ist das Betriebssystem gefordert, hier andere Tätigkeiten zu veranlassen. Welche fallen dir ein? | * Eigentlich ist das Betriebssystem gefordert, hier andere Tätigkeiten zu veranlassen. Welche fallen dir ein? | ||

</p> | </p> | ||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Aufgabe 3"> | |||

<p> | <p> | ||

Im [http://youtu.be/nOEW4I_QX2c Video] wird darauf verzichtet zu zeigen, wie sich Werte beispielsweise in den Registern PC oder IR (usw.) ändern, und welche Werte davon über das Bussystem übertragen werden. | Im [http://youtu.be/nOEW4I_QX2c Video] wird darauf verzichtet zu zeigen, wie sich Werte beispielsweise in den Registern PC oder IR (usw.) ändern, und welche Werte davon über das Bussystem übertragen werden. | ||

| Zeile 198: | Zeile 205: | ||

* Was passiert mit diesen Registern am Ende der Abarbeitung der Interruptbehandlungsroutine (wenn im [http://youtu.be/nOEW4I_QX2c Video] das ACK-IRQ-Signal zum Interrupt-Controller gesendet wird)? | * Was passiert mit diesen Registern am Ende der Abarbeitung der Interruptbehandlungsroutine (wenn im [http://youtu.be/nOEW4I_QX2c Video] das ACK-IRQ-Signal zum Interrupt-Controller gesendet wird)? | ||

</p> | </p> | ||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Aufgabe 4"> | |||

<p> | <p> | ||

Das Zustandsregister eines Controllers kann (u.a.) ein READY anzeigen, im [http://youtu.be/nOEW4I_QX2c Video] ist das zu sehen. Es reicht ein Bit, um den Zustand READY zu kennzeichnen. Ist dieses Bit gleich 1, so gilt: der Controller ist READY für den nächsten Steuerbefehl. Gleiches gilt für den Zustand BUSY. Auch hierfür reicht ein Bit. | Das Zustandsregister eines Controllers kann (u.a.) ein READY anzeigen, im [http://youtu.be/nOEW4I_QX2c Video] ist das zu sehen. Es reicht ein Bit, um den Zustand READY zu kennzeichnen. Ist dieses Bit gleich 1, so gilt: der Controller ist READY für den nächsten Steuerbefehl. Gleiches gilt für den Zustand BUSY. Auch hierfür reicht ein Bit. | ||

| Zeile 212: | Zeile 221: | ||

* Welche Alternative fällt dir ein? | * Welche Alternative fällt dir ein? | ||

</p> | </p> | ||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Aufgabe 5"> | |||

<p> | <p> | ||

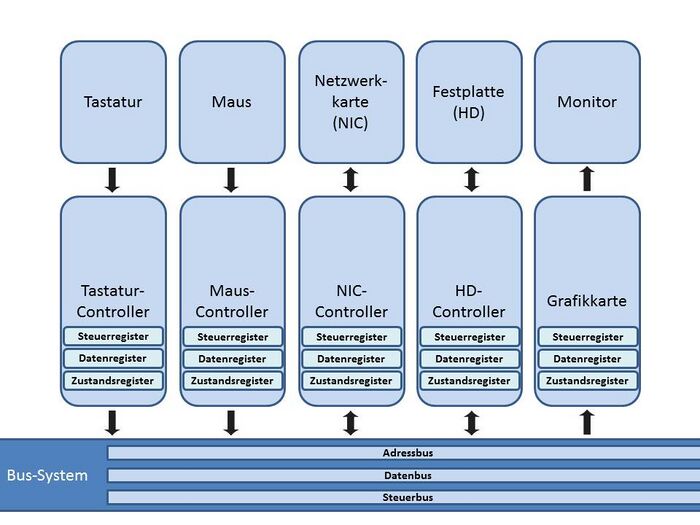

Im Text dieser Seite wird erwähnt, dass die im Bild gezeigten Controller nur ein Register je Typ enthalten, dass es aber auch möglich ist, dass ein Controller mehrere Register eines Typs enthält. | Im Text dieser Seite wird erwähnt, dass die im Bild gezeigten Controller nur ein Register je Typ enthalten, dass es aber auch möglich ist, dass ein Controller mehrere Register eines Typs enthält. | ||

* Entwickle ein Szenario, in dem es sinnvoll mehrere Register eines Typs gibt! | * Entwickle ein Szenario, in dem es sinnvoll mehrere Register eines Typs gibt! | ||

</p> | </p> | ||

</loop_task> | |||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

Version vom 24. September 2013, 11:06 Uhr

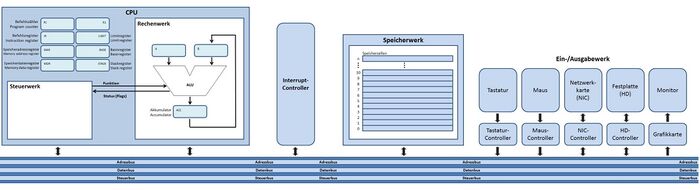

Im bisherigen Verlauf dieses Moduls sind bereits viele Beispiele gezeigt worden, bei denen das Steuerwerk der CPU mit Registern oder dem Hauptspeicher kommuniziert. Da ein Computer aber noch weitere Komponenten besitzt, muss auch die Kommunikation der CPU mit den sogenannten Peripheriegeräten möglich sein.

Peripheriegeräte sind beispielsweise:

- Festplatte

- Monitor

- Maus

- Tastatur

- etc.

Genaugenommen kommuniziert die CPU dann nicht direkt mit diesen Komponenten, sondern mit einem Controller, der speziell für die betreffende Komponente zuständig ist.

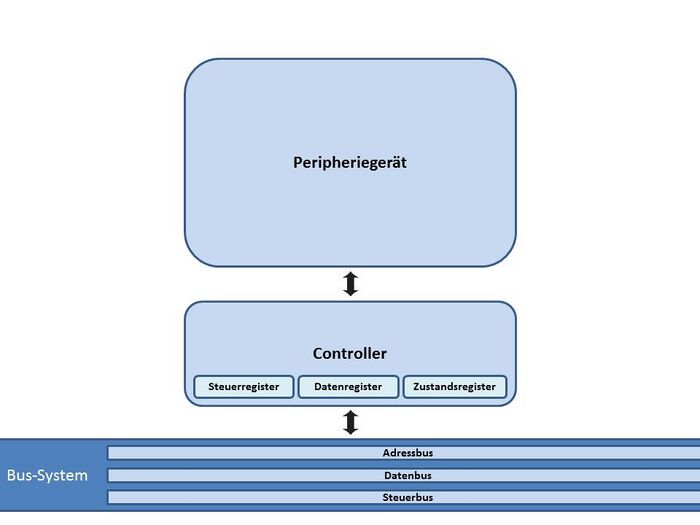

Allgemeiner Aufbau eines Controllers

Genau wie die CPU besitzt auch der Controller eines Peripheriegeräts verschiedene Register. Üblich sind:

- Steuerregister

Hier kann über das Bussystem ein Steuerbefehl an den Controller übergeben werden (ähnlich dem Befehlsregister auf der CPU). - Datenregister

Hier kann ein Datenwort hinterlegt, oder ein vom Peripheriegerät über den Controller bereitgestelltes Datenwort ausgelesen werden. - Zustandsregister

Hier hinterlegt der Controller jeweils Werte, die über den aktuellen Zustand des Controllers (oder Peripheriegeräts) Auskunft geben.

In dem (oder den) Zustandsregister(n) können verschiedene Zustände angezeigt werden, beispielsweise

- Ready: Controller ist bereit für den nächsten Steuerbefehl.

- Busy: Controller ist noch mit der Ausführung des aktuellen Steuerbefehls beschäftigt.

- Read Error: Das angeforderte Datenwort kann nicht vom Peripheriegerät gelesen werden.

- Write Error: Das im Datenregister befindliche Datenwort kann nicht auf dem Peripheriegerät gespeichert werden.

- Out of paper: Der an diesen Controller angeschlossene Drucker hat kein Papier mehr.

- etc.

Die folgende Abbildung zeigt den allgemeinen Aufbau eines Controllers. Dabei ist von jeder Registerart nur ein einziges eingezeichnet, es ist jedoch auch denkbar, dass der Controller über mehrere Register je Art verfügt.

Die bislang betrachte Menge an Peripheriegeräten verfügt jeweils über einen eigenen Controller, wobei jeder Controller mit dem entsprechenden Registersatz ausgestattet ist:

Auf das Datenregister eines Controllers kann die CPU sowohl lesend, als auch schreibend zugreifen. Wie verhält es sich aber beim Steuer- und beim Zustandsregister? Ist der Zugriff hier nur lesend, nur schreibend oder lesend und schreibend möglich?

Zeit und Kosten machen den Unterschied

Zwei entscheidende Unterschiede bei der Kommunikation zwischen dem Steuerwerk und Registern, Hauptspeicher sowie den Controllern der weiteren Komponenten bestehen einerseits in der dafür benötigten Zeit, und andererseits in den Kosten, die eine technische Realisierung der betreffenden Komponenten verursacht.

Die Kommunikation zwischen Steuerwerk und Registern ist mit Abstand am schnellsten möglich. Beides ist auf der CPU angesiedelt, die Wege sind kurz und effizient ausgebaut. Nachteilig ist lediglich, dass alle Register der CPU zusammen nur recht wenig Speicherplatz bieten. Dies liegt an entsprechend hohen Kosten, welche die Integration (vieler) weiterer Register auf der CPU nach sich ziehen würde.

Wunschvorstellung

Wäre es nicht ideal, wenn alle Programme und Daten, die du normalerweise auf deiner Festplatte gespeichert hast, direkt in Registern der CPU abgelegt wären? Du bräuchtest dann weder Festplatte noch Hauptspeicher und dein System würde konkurrenzlos schnell arbeiten!

Du kannst dir ausmalen, dass das technisch nicht so einfach möglich ist, oder?

Die Kommunikation zwischen Steuerwerk und Hauptspeicher ist - verglichen mit den Registern - bereits deutlich langsamer, jedoch immer noch recht schnell. Der Hauptspeicher ist speziell für eine schnelle Arbeitsweise konzipiert, er bietet auch deutlich mehr Platz als die Menge der CPU-Register. Nachteilig ist hier, dass der Inhalt des Hauptspeichers verloren geht, sobald der betreffende Computer ausgeschaltet wird.

Abhilfe schafft bei diesem Nachteil beispielsweise die Festplatte. Sie bietet üblicherweise deutlich mehr Speicherplatz als der Hauptspeicher und kann ihre Daten zudem dauerhaft (also auch über ein Ausschalten und einen Neustart des betreffenden Rechners hinaus) speichern. Leider ist die Kommunikation zwischen CPU und Festplatten-Controller erheblich langsamer als zwischen CPU und Hauptspeicher. Dafür liegen die Kosten für eine Festplatte (in Bezug zur Speicherkapazität) deutlich unter den Kosten für Hauptspeicher.

Eine Festplatte kostet pro Gigabyte Speicherkapazität deutlich weniger, als ein Gigabyte Hauptspeicher. Dafür arbeitet der Hauptspeicher deutlich schneller.

Tanenbaum 2009 nennt folgende näherungsweisen Vergleichswerte für die Zugriffe auf Daten:

- Die CPU kann 10 x schneller auf ein Register zugreifen, als auf den Arbeitsspeicher.

- Die CPU kann 1 000 x schneller auf den Arbeitsspeicher zugreifen, als auf eine Festplatte.

- Ein Registerzugriff ist damit 10 000 x schneller, als ein Festplattenzugriff.

Auch für die Kommunikation zwischen der CPU und allen weiteren Controllern der sonstigen Komponenten gilt: Es ist langsam.

Datentransfer und Interrupts

Das folgende Video erläutert die Bedeutung von Interrupts bei der Kommunikation zwischen CPU und Ein-/ Ausgabegeräten. Beispielhaft wird die Festplatte als E/A-Gerät betrachtet.

Im Video wird deutlich, dass für jedes einzelne Datenwort folgende Schritte erforderlich sind:

- Die CPU sendet die Adresse des gewünschten Datenwortes an den Festplatten-Controller.

- Der Festplatten-Controller besorgt das Datenwort von der Festplatte und stellt es in seinem Datenregister zur Verfügung.

- Der Festplatten-Controller sendet einen Interrupt zum Interrupt-Controller.

- Der Interrupt-Controller nimmt den Interrupt entgegen und verwaltet ihn.

- Der Interrupt-Controller informiert die CPU über den Interrupt des Festplatten-Controllers.

- Die CPU startet die zugehörige Interruptbehandlungsroutine.

- Die Behandlungsroutine kopiert das Datenwort in ein Register auf der CPU.

- Die Behandlungsroutine sendet das Datenwort von der CPU zum Hauptspeicher.

- Der Hauptspeicher legt das Datenwort in der gewünschten Speicherzelle ab.

- Die Interruptbehandlungsroutine informiert den Interrupt-Controller darüber, dass der Interrupt jetzt fertig behandelt ist.

Ganz schön viel Aufwand, oder? (Und dabei ist diese Auflistung noch nicht einmal ganz komplett, aber damit beschäftigst du dich gleich noch in den Aufgaben weiter unten ;-)

Für eine Handvoll Bits...

Es ist an dieser Stelle wichtig zu erkennen, was für ein großer Aufwand betrieben wird, nur um ein einzelnes Datenwort von der Festplatte in den Hauptspeicher zu kopieren.

Aber: Wie groß ist so ein Datenwort eigentlich?

Es hat die Größe der Registerbreite des Datenregisters auf dem Festplatten-Controller, oder alternativ die Größe der Busbreite des Datenbusses, über das es übertragen wird. Mit hoher Wahrscheinlichkeit haben Register und Bus dieselbe Breite, vielleicht 32 oder 64 Bit (und auf neueren Systemen irgendwann mal 128 Bit).

Und: Wie groß ist heute eine übliche Datei, die ein Anwendungsprogramm enthält?

Das können schnell mehrere Megabyte sein, also ganz schön viele Datenwörter...

Weiterführende Literatur

erläutert in Kapitel 5 (Ein- und Ausgabe) weitere Hintergründe zum Thema. Die Lektüre dieser Quelle sei ausdrücklich empfohlen.

Studierende sind oftmals berechtigt, eine PDF-Version dieses Buches ohne entstehende Kosten über ihre Hochschulen von Springerlink zu beziehen.

Im Video wird gezeigt, wie die CPU wartet, und wartet, und wartet. Das ist natürlich keine gute Idee im Hinblick auf die Geschwindigkeit des Gesamtsystems.

- Was könnte die CPU alternativ tun, während sie auf den Interrupt wartet?

- Eigentlich ist das Betriebssystem gefordert, hier andere Tätigkeiten zu veranlassen. Welche fallen dir ein?

Im Video wird darauf verzichtet zu zeigen, wie sich Werte beispielsweise in den Registern PC oder IR (usw.) ändern, und welche Werte davon über das Bussystem übertragen werden.

- Diskutiere dieses in deiner Lerngruppe!

- Erklärt euch gegenseitig das Zusammenspiel aller Komponenten und Register.

- Findest du auch ein Beispiel, welches die ALU einbezieht?

- Was passiert mit PC und IR bei einem Interrupt?

- Wie werden diese Register beim Abarbeiten der Interruptbehandlungsroutine belegt?

- Was passiert mit diesen Registern am Ende der Abarbeitung der Interruptbehandlungsroutine (wenn im Video das ACK-IRQ-Signal zum Interrupt-Controller gesendet wird)?

Das Zustandsregister eines Controllers kann (u.a.) ein READY anzeigen, im Video ist das zu sehen. Es reicht ein Bit, um den Zustand READY zu kennzeichnen. Ist dieses Bit gleich 1, so gilt: der Controller ist READY für den nächsten Steuerbefehl. Gleiches gilt für den Zustand BUSY. Auch hierfür reicht ein Bit.

Für READY und BUSY werden im Zustandsregister demnach zwei Bit benötigt.

- Kannst du dem zustimmen?

- Oder gibt es eine sinnvolle Alternative?

- Welche Alternative fällt dir ein?

Im Text dieser Seite wird erwähnt, dass die im Bild gezeigten Controller nur ein Register je Typ enthalten, dass es aber auch möglich ist, dass ein Controller mehrere Register eines Typs enthält.

- Entwickle ein Szenario, in dem es sinnvoll mehrere Register eines Typs gibt!

Diese Seite steht unter der Creative Commons Namensnennung 3.0 Unported Lizenz http://i.creativecommons.org/l/by/3.0/80x15.png