2.1.3.2 Speicherwerk

| [gesichtete Version] | [gesichtete Version] |

(Die 3 letzten Textänderungen von Trojafrank und Scharmorit wurden verworfen und die Version 4556 von Habertja wiederhergestellt.) |

(LOOP2 Upgrade) |

||

| Zeile 7: | Zeile 7: | ||

== Definition: Speicherwerk == | == Definition: Speicherwerk == | ||

<p> | <p> | ||

<loop_index>Speicherwerk</loop_index> | <loop_index id="5fa9787eaf972">Speicherwerk</loop_index> | ||

<loop_area type="definition"> | <loop_area type="definition"> | ||

<p> | <p> | ||

| Zeile 16: | Zeile 16: | ||

<p> | <p> | ||

Das Speicherwerk gehört zu den sogenannten "<loop_index>flüchtiger Speicher|Speicher, flüchtiger</loop_index>flüchtigen Speichern". Es kann nur Informationen speichern, solange es mit Strom versorgt wird, also bei eingeschaltetem Rechner. Sobald der Rechner ausgeschaltet wird, gehen alle im Speicherwerk abgelegten Informationen unwiederbringlich verloren. | Das Speicherwerk gehört zu den sogenannten "<loop_index id="5fa9787eaf980">flüchtiger Speicher|Speicher, flüchtiger</loop_index>flüchtigen Speichern". Es kann nur Informationen speichern, solange es mit Strom versorgt wird, also bei eingeschaltetem Rechner. Sobald der Rechner ausgeschaltet wird, gehen alle im Speicherwerk abgelegten Informationen unwiederbringlich verloren. | ||

</p> | </p> | ||

<br /> | <br /> | ||

<p> | <p> | ||

<loop_index>RAM|Random Access Memory</loop_index> | <loop_index id="5fa9787eaf98c">RAM|Random Access Memory</loop_index> | ||

<loop_area type="notice"> | <loop_area type="notice"> | ||

<p> | <p> | ||

| Zeile 32: | Zeile 32: | ||

== Definition: Arbeitsweise des Speicherwerks == | == Definition: Arbeitsweise des Speicherwerks == | ||

<p> | <p> | ||

<loop_index>Arbeitsweise, Speicherwerk|Speicherwerk, Arbeitsweise</loop_index> | <loop_index id="5fa9787eaf997">Arbeitsweise, Speicherwerk|Speicherwerk, Arbeitsweise</loop_index> | ||

<loop_area type="definition"> | <loop_area type="definition"> | ||

<p> | <p> | ||

| Zeile 52: | Zeile 52: | ||

<p> | <p> | ||

<loop_area icon="Video.png" icontext="Video"> | <loop_area icon="Video.png" icontext="Video"> | ||

<loop_media type="video" title="Arbeitsweise des Speicherwerks (02:06)" description="http://youtu.be/pefqk2C7wgw" copyright="CC-BY" index=true show_copyright=true>{{#ev:youtube|pefqk2C7wgw|700}}</loop_media> | <loop_media type="video" title="Arbeitsweise des Speicherwerks (02:06)" description="http://youtu.be/pefqk2C7wgw" copyright="CC-BY" index=true show_copyright=true id="5fa9787eaf9a3">{{#ev:youtube|pefqk2C7wgw|700}}</loop_media> | ||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

| Zeile 60: | Zeile 60: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Speicherzelle 3"> | <loop_task title="Speicherzelle 3" id="5fa9787eaf9ad"> | ||

<p> | <p> | ||

Zu Beginn des Videos empfängt das Speicherwerk über den Adressbus die Adresse "00000011". Warum wird damit Speicherzelle 3 angesprochen? | Zu Beginn des Videos empfängt das Speicherwerk über den Adressbus die Adresse "00000011". Warum wird damit Speicherzelle 3 angesprochen? | ||

| Zeile 80: | Zeile 80: | ||

== Definition: Steuerbus == | == Definition: Steuerbus == | ||

<p> | <p> | ||

<loop_index>Steuerbus|Bus, Steuerbus</loop_index> | <loop_index id="5fa9787eaf9b8">Steuerbus|Bus, Steuerbus</loop_index> | ||

<loop_area type="definition"> | <loop_area type="definition"> | ||

<p> | <p> | ||

| Zeile 89: | Zeile 89: | ||

<p> | <p> | ||

Die <loop_index>Breite, Steuerbus|Steuerbus, Breite</loop_index>Breite des Steuerbusses kann sich deutlich von der <loop_index>Breite, Adressbus|Adressbus, Breite</loop_index>Breite des Adress- oder <loop_index>Breite, Datenbus|Datenbus, Breite</loop_index>Datenbusses unterscheiden. In der Regel ist die Breite des Steuerbusses geringer. | Die <loop_index id="5fa9787eaf9c4">Breite, Steuerbus|Steuerbus, Breite</loop_index>Breite des Steuerbusses kann sich deutlich von der <loop_index id="5fa9787eaf9ce">Breite, Adressbus|Adressbus, Breite</loop_index>Breite des Adress- oder <loop_index id="5fa9787eaf9d9">Breite, Datenbus|Datenbus, Breite</loop_index>Datenbusses unterscheiden. In der Regel ist die Breite des Steuerbusses geringer. | ||

</p> | </p> | ||

| Zeile 98: | Zeile 98: | ||

<p> | <p> | ||

<loop_figure title="Speicherwerk mit Bus-System" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Speicherwerk.jpg|700px]]</loop_figure> | <loop_figure title="Speicherwerk mit Bus-System" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9787eaf9e4">[[Datei:Speicherwerk.jpg|700px]]</loop_figure> | ||

</p> | </p> | ||

| Zeile 106: | Zeile 106: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Von dezimal zu binär"> | <loop_task title="Von dezimal zu binär" id="5fa9787eaf9f0"> | ||

<p> | <p> | ||

Im Bild oben siehst du das Speicherwerk mit seinen von 0 bis n nummerierten Speicherzellen. Diese Nummerierung ist angegeben in '''dezimalen''' Zahlen, das Speicherwerk verarbeitet aber in der Realität nur '''binär''' angegebene Adressen. Ändere deshalb die Nummerierung der einzelnen Speicherzellen in eine binäre Schreibweise ab! | Im Bild oben siehst du das Speicherwerk mit seinen von 0 bis n nummerierten Speicherzellen. Diese Nummerierung ist angegeben in '''dezimalen''' Zahlen, das Speicherwerk verarbeitet aber in der Realität nur '''binär''' angegebene Adressen. Ändere deshalb die Nummerierung der einzelnen Speicherzellen in eine binäre Schreibweise ab! | ||

| Zeile 116: | Zeile 116: | ||

<p> | <p> | ||

<loop_figure title="Abbildung zu Aufgabe 2" description="" copyright="CC-BY" index=true show_copyright=true> | <loop_figure title="Abbildung zu Aufgabe 2" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9787eaf9fa"> | ||

<p id="MeinLink"> | <p id="MeinLink"> | ||

[[Datei:Speicherwerk2.jpg]] | [[Datei:Speicherwerk2.jpg]] | ||

| Zeile 130: | Zeile 130: | ||

<p id="Aufgabe 3: Die 4 GiB-Grenze"> | <p id="Aufgabe 3: Die 4 GiB-Grenze"> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Die 4 GiB-Grenze"> | <loop_task title="Die 4 GiB-Grenze" id="5fa9787eafa05"> | ||

<p> | <p> | ||

In der Vergangenheit war immer wieder folgender Satz zu hören: ''"Ein 32-Bit-Betriebssystem kann maximal 4 [[GiB,_MiB,_KiB_im_Vergleich_zu_GB,_MB,_KB|GiB]] Arbeitsspeicher (RAM) verwalten"''. Gehen wir für unser Speicherwerk davon aus, dass der Adressbus eine Breite von 32 Bit besitzt. Damit können dann auch maximal 4 [[GiB,_MiB,_KiB_im_Vergleich_zu_GB,_MB,_KB|GiB]] im Speicherwerk angesprochen werden. | In der Vergangenheit war immer wieder folgender Satz zu hören: ''"Ein 32-Bit-Betriebssystem kann maximal 4 [[GiB,_MiB,_KiB_im_Vergleich_zu_GB,_MB,_KB|GiB]] Arbeitsspeicher (RAM) verwalten"''. Gehen wir für unser Speicherwerk davon aus, dass der Adressbus eine Breite von 32 Bit besitzt. Damit können dann auch maximal 4 [[GiB,_MiB,_KiB_im_Vergleich_zu_GB,_MB,_KB|GiB]] im Speicherwerk angesprochen werden. | ||

| Zeile 139: | Zeile 139: | ||

<p> | <p> | ||

<loop_figure title="Abbildung zu Aufgabe 4" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Speicher32bit.jpg]]</loop_figure> | <loop_figure title="Abbildung zu Aufgabe 4" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9787eafa0f">[[Datei:Speicher32bit.jpg]]</loop_figure> | ||

</p> | </p> | ||

<p> | <p> | ||

| Zeile 152: | Zeile 152: | ||

== Memory Address Register und Memory Data Register == | == Memory Address Register und Memory Data Register == | ||

<p> | <p> | ||

<loop_index>Speicheradressregister|Memory Address Register|MAR|Speicherdatenregister|Memory Data Register|MDR</loop_index> | <loop_index id="5fa9787eafa1b">Speicheradressregister|Memory Address Register|MAR|Speicherdatenregister|Memory Data Register|MDR</loop_index> | ||

Um die Zusammenarbeit zwischen dem Speicherwerk und der CPU bzw. dem Steuerwerk zu vereinfachen, werden auf der CPU oftmals spezielle Register verwendet, welche ausschließlich für die Kommunikation mit dem Speicherwerk zuständig sind. Dies sind das '''Speicheradressregister''' ('''Memory Address Register''', kurz '''MAR'''), sowie das '''Speicherdatenregister''' ('''Memory Data Register''', kurz '''MDR'''). | Um die Zusammenarbeit zwischen dem Speicherwerk und der CPU bzw. dem Steuerwerk zu vereinfachen, werden auf der CPU oftmals spezielle Register verwendet, welche ausschließlich für die Kommunikation mit dem Speicherwerk zuständig sind. Dies sind das '''Speicheradressregister''' ('''Memory Address Register''', kurz '''MAR'''), sowie das '''Speicherdatenregister''' ('''Memory Data Register''', kurz '''MDR'''). | ||

</p> | </p> | ||

| Zeile 173: | Zeile 173: | ||

<p> | <p> | ||

<loop_area type="task"> | <loop_area type="task"> | ||

<loop_task title="Der Weg der Daten"> | <loop_task title="Der Weg der Daten" id="5fa9787eafa24"> | ||

<p> | <p> | ||

Betrachte die Situation, in der die momentan im PC (Befehlszähler) gespeicherte Adresse an das Speicherwerk übermittelt wird, um so den nächsten Befehl aus der adressierten Speicherzelle in das IR (Befehlsregister) zu kopieren. | Betrachte die Situation, in der die momentan im PC (Befehlszähler) gespeicherte Adresse an das Speicherwerk übermittelt wird, um so den nächsten Befehl aus der adressierten Speicherzelle in das IR (Befehlsregister) zu kopieren. | ||

| Zeile 181: | Zeile 181: | ||

<p> | <p> | ||

<loop_figure title="Abbildung zu Aufgabe 4" description="" copyright="CC-BY" index=true show_copyright=true>[[Datei:Cpu8-speicher.jpg|650px]]</loop_figure></p> | <loop_figure title="Abbildung zu Aufgabe 4" description="" copyright="CC-BY" index=true show_copyright=true id="5fa9787eafa2f">[[Datei:Cpu8-speicher.jpg|650px]]</loop_figure></p> | ||

</loop_task> | </loop_task> | ||

</loop_area> | </loop_area> | ||

</p> | </p> | ||

Version vom 9. November 2020, 19:12 Uhr

Speicherwerk

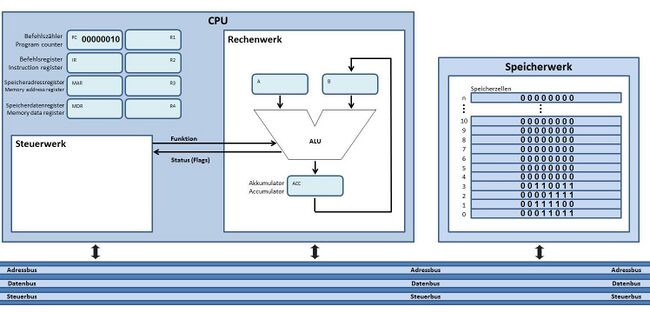

Das Speicherwerk ist ein Bestandteil der Von-Neumann-Architektur:

Definition: Speicherwerk

Das Speicherwerk ist in eine endliche Anzahl gleichgroßer (aber verhältnismäßig kleiner) Speicherzellen unterteilt. Jede Zelle verfügt dabei über eine eindeutige Adresse. Alle Adressen sind fortlaufend, beginnend bei Null (0, 1, 2, 3, ...).

Das Speicherwerk gehört zu den sogenannten "flüchtigen Speichern". Es kann nur Informationen speichern, solange es mit Strom versorgt wird, also bei eingeschaltetem Rechner. Sobald der Rechner ausgeschaltet wird, gehen alle im Speicherwerk abgelegten Informationen unwiederbringlich verloren.

Auf deinem eigenen PC oder Laptop entspricht der RAM (Random Access Memory) dem Speicherwerk.

Definition: Arbeitsweise des Speicherwerks

Das Speicherwerk kann den Wert einer adressierten Speicherstelle auslesen und zur Verfügung stellen oder andersherum einen zur Verfügung gestellten Wert in einer adressierten Speicherstelle ablegen.

Lesen oder Schreiben?

Diese Definition der Arbeitsweise ist an einer Stelle noch etwas ungenau. Woher weiß das Speicherwerk, ob es die adressierte Zelle auslesen oder überschreiben soll?

Das folgende Video geht näher darauf ein.

Aufgabe 1

Zu Beginn des Videos empfängt das Speicherwerk über den Adressbus die Adresse "00000011". Warum wird damit Speicherzelle 3 angesprochen?

(Entschuldigung! Diese Frage ist für Studierende im ersten Semester bestimmt. Falls Du bereits in einem höheren Semester bist, ist sie natürlich viel zu leicht.) ;-)

Aus dem Video folgt noch eine Definition:

Definition: Steuerbus

Ein Steuerbus ist ein Bus, bei dem die parallel übertragene Gruppe von Bits als Steuerinformation zu interpretieren ist.

Die Breite des Steuerbusses kann sich deutlich von der Breite des Adress- oder Datenbusses unterscheiden. In der Regel ist die Breite des Steuerbusses geringer.

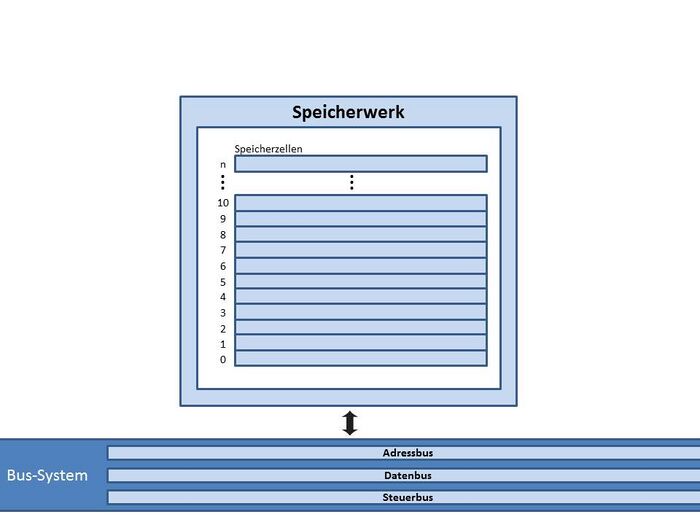

Das im Video erläuterte Speicherwerk mit dem erweiterten Bus-System zeigt die folgende Abbildung:

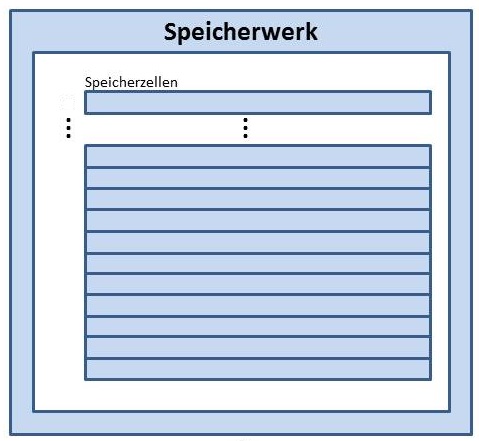

Aufgabe 2

Im Bild oben siehst du das Speicherwerk mit seinen von 0 bis n nummerierten Speicherzellen. Diese Nummerierung ist angegeben in dezimalen Zahlen, das Speicherwerk verarbeitet aber in der Realität nur binär angegebene Adressen. Ändere deshalb die Nummerierung der einzelnen Speicherzellen in eine binäre Schreibweise ab!

Interessant ist, welche binäre Adresse du der Speicherzelle n gibst. Entscheide dich für eine konkrete binäre Adresse und erläutere deine Entscheidung in deiner Lerngruppe! (Es gibt für Speicherzelle n nicht "die eine richtige" binäre Adresse. Es kommt aber darauf an, eine sinnvolle und nachvollziehbare Begründung für die getroffene Entscheidung zu geben.)

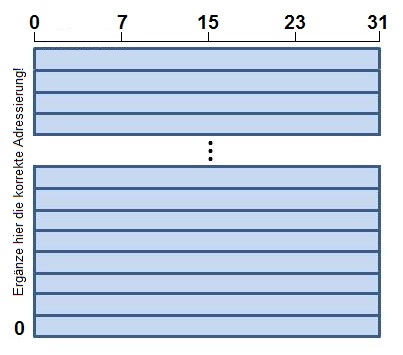

Aufgabe 3

In der Vergangenheit war immer wieder folgender Satz zu hören: "Ein 32-Bit-Betriebssystem kann maximal 4 GiB Arbeitsspeicher (RAM) verwalten". Gehen wir für unser Speicherwerk davon aus, dass der Adressbus eine Breite von 32 Bit besitzt. Damit können dann auch maximal 4 GiB im Speicherwerk angesprochen werden.

- Wie viele Adressen können mit 32 Bit unterschieden werden? (Das Ergebnis gibt dann gleichzeitig die Anzahl der Speicherzellen im Speicherwerk an.)

- Wie viele Bit besitzt eine einzige Speicherzelle unter Berücksichtigung der 4 GiB Gesamtspeichermenge und dem Hinweis zur Bedeutung von "GiB"?

- Gehen wir weiter davon aus, dass der Datenbus ebenfalls 32 Bit breit ist.

Beim Eintreffen einer Adresse über den Adressbus am Speicherwerk und dem Befehl "Lesen" auf dem Steuerbus wird das Speicherwerk über den Datenbus genau 32 Bit zurücksenden. Der Speicher kann dann in einer Skizze mit Zellen gezeichnet werden, die jeweils eine Breite von 32 Bit besitzen.

Wie lautet die korrekte Adressierung dieser 32 Bit breiten Zellen? (Gib die Adressierung sowohl in dezimaler, als auch in binärer Schreibweise an!)

- Wenn eine Speicherzelle in der Abbildung eine Breite von 32 Bit besitzt, warum wird oben im Bild nur bis 31 gezählt?

Memory Address Register und Memory Data Register

Um die Zusammenarbeit zwischen dem Speicherwerk und der CPU bzw. dem Steuerwerk zu vereinfachen, werden auf der CPU oftmals spezielle Register verwendet, welche ausschließlich für die Kommunikation mit dem Speicherwerk zuständig sind. Dies sind das Speicheradressregister (Memory Address Register, kurz MAR), sowie das Speicherdatenregister (Memory Data Register, kurz MDR).

Im MAR legt das Steuerwerk jeweils die Adresse ab, welche im Speicherwerk angesprochen werden soll. Bei einem Lesezugriff auf die Speicherzelle wird der vom Speicherwerk über den Datenbus bereitgestellte Wert im MDR abgelegt und kann von hier aus weiter verarbeitet werden. Bei einem Schreibzugriff muss sich im MDR der zu schreibende Wert befinden, so dass er über den Datenbus an das Speicherwerk übermittelt werden kann.

Die Existenz der beiden Register (MAR und MDR) macht deutlich mehr Sinn, wenn du dir vorstellst, dass es (neben dem "normalen" Bus der Von-Neumann-Architektur) noch einen speziellen weiteren Bus zwischen eben diesen beiden Registern und dem Speicherwerk gibt. Auf das Einzeichnen dieses zusätzlichen Busses wird in diesem Modul der Einfachheit halber jedoch verzichtet.

Aufgabe 4

Betrachte die Situation, in der die momentan im PC (Befehlszähler) gespeicherte Adresse an das Speicherwerk übermittelt wird, um so den nächsten Befehl aus der adressierten Speicherzelle in das IR (Befehlsregister) zu kopieren.

- Welches Signal wird am Steuerbus angelegt?

- Welchen Weg nehmen die jeweiligen Daten, wenn zur direkten Kommunikation zwischen CPU und Speicherwerk nur MAR und MDR eingesetzt werden dürfen? Erläutere deinen Weg in deiner Lerngruppe!